Thursday, February 27th 2020

AMD Gives Itself Massive Cost-cutting Headroom with the Chiplet Design

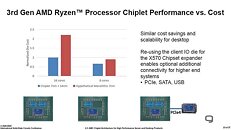

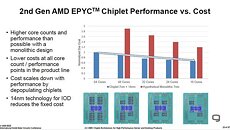

At its 2020 IEEE ISSCC keynote, AMD presented two slides that detail the extent of cost savings yielded by its bold decision to embrace the MCM (multi-chip module) approach to not just its enterprise and HEDT processors, but also its mainstream desktop ones. By confining only those components that tangibly benefit from cutting-edge silicon fabrication processes, namely the CPU cores, while letting other components sit on relatively inexpensive 12 nm, AMD is able to maximize its 7 nm foundry allocation, by making it produce small 8-core CCDs (CPU complex dies), which add up to AMD's target core-counts. With this approach, AMD is able to cram up to 16 cores onto its AM4 desktop socket using two chiplets, and up to 64 cores using eight chiplets on its SP3r3 and sTRX4 sockets.

In the slides below, AMD compares the cost of its current 7 nm + 12 nm MCM approach to a hypothetical monolithic die it would have had to build on 7 nm (including the I/O components). The slides suggest that the cost of a single-chiplet "Matisse" MCM (eg: Ryzen 7 3700X) is about 40% less than that of the double-chiplet "Matisse" (eg: Ryzen 9 3950X). Had AMD opted to build a monolithic 7 nm die that had 8 cores and all the I/O components of the I/O die, such a die would cost roughly 50% more than the current 1x CCD + IOD solution. On the other hand, a monolithic 7 nm die with 16 cores and I/O components would cost 125% more. AMD hence enjoys a massive headroom for cost-cutting. Prices of the flagship 3950X can be close to halved (from its current $749 MSRP), and AMD can turn up the heat on Intel's upcoming Core i9-10900K by significantly lowering price of its 12-core 3900X from its current $499 MSRP. The company will also enjoy more price-cutting headroom for its 6-core Ryzen 5 SKUs than it did with previous-generation Ryzen 5 parts based on monolithic dies.

Source:

Guru3D

In the slides below, AMD compares the cost of its current 7 nm + 12 nm MCM approach to a hypothetical monolithic die it would have had to build on 7 nm (including the I/O components). The slides suggest that the cost of a single-chiplet "Matisse" MCM (eg: Ryzen 7 3700X) is about 40% less than that of the double-chiplet "Matisse" (eg: Ryzen 9 3950X). Had AMD opted to build a monolithic 7 nm die that had 8 cores and all the I/O components of the I/O die, such a die would cost roughly 50% more than the current 1x CCD + IOD solution. On the other hand, a monolithic 7 nm die with 16 cores and I/O components would cost 125% more. AMD hence enjoys a massive headroom for cost-cutting. Prices of the flagship 3950X can be close to halved (from its current $749 MSRP), and AMD can turn up the heat on Intel's upcoming Core i9-10900K by significantly lowering price of its 12-core 3900X from its current $499 MSRP. The company will also enjoy more price-cutting headroom for its 6-core Ryzen 5 SKUs than it did with previous-generation Ryzen 5 parts based on monolithic dies.

89 Comments on AMD Gives Itself Massive Cost-cutting Headroom with the Chiplet Design

I wonder how this compares to manufacturing cost of Intel mainstream CPUs? For example 8-core like 9900K with die size of 175mm^2.It doesn't. Renoir is monolithic.Not halved. Renoir has 1/4 L3$ of Matisse. 3700X has 32MB L3$ (and 3900/3950X have 64MB), 4800H has 8MB.

I am willing to bet this is thanks to Integrated Memory Controller.

Edit:

What strikes me as odd is how comparatively small the manufacturing cost saving is for EPYCs. I mean, half the cost is nothing to sneeze at but with everything that is said I expected this to be bigger.

On the other hand, EPYC's massive IOD probably has a large part to play here.

Edit:

By the way, IOD on EPYC is 430mm^2.

For comparison, Intel Skylake-SP HCC (18 cores) is 484mm^2.This is based on what? I get that this is an assumption but there is nothing in this story to support it. Sure, AMD can drop pices as they have a very good profit margin. So can Intel. Manufacturing costs do not play as much into pricing equation on desktop.

So what AMD is really saying: we decided to base our competitive advantage on a very expensive manufacturing process and going with MCM was the only way we could afford it.

And yeah... it makes you wonder how much AMD asks for (and earns from) these 8-core mobile SoCs.

Gross margin tells you how much it costs to make a product, i.e.:

(revenue - cost of goods sold) / revenue

In case of AMD majority of "cost of goods sold" is what they pay for outsourced manufacturing. It doesn't include things like R&D.

This ratio is growing, but it's still much lower than Intel's (and Nvidia's).

In other words: despite MCM and more dense node, it still costs them more to make chips than it costs Intel and Nvidia.

And combining that and what they say about MCM saving, it suggests that they're losing money on large 7nm monolithic chips (4800U will be as big as two Zen2 chiplets).

As long as there are stupid consumers who invest in anything Intel, it will be the same story.Intel's N14 process is already more than 5-year-old, hence the manufacturing cost should be very low, including the economy of scale.

No-one have to pay full price from intel, very far from it.

No-one gets serious rebate on amd cpu's.

www.anandtech.com/show/15381/amd-ryzen-mobile-4000-measuring-renoirs-die-size

I doubt clocks are influenced by the number of chips, but latency is.

Still, I'm a little surprised no one is mentioning what looks to me like the #1 space saving measure AMD took: not wasting 30% die space on an IGP.