Apple to Launch Arm-Powered MacBook in the next 18 Months

Apple is currently designing a custom series of CPUs, for its Macbook laptop lineup, based on the Arm Instruction Set Architecture. Having designed some of the most powerful mobile processors that are inside the iPhone series of devices, Apple is preparing to make a jump to an even more powerful device lineup by bringing custom CPUs for MacBook. Tired of the speed by which Intel replaces and upgrades its Core lineup of CPUs, Apple decided to take the matter in its own hands and rumors about the switch to a custom solution have been going on for a while. However, we now have some information about when to expect the first wave of Arm-powered Macs.

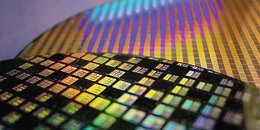

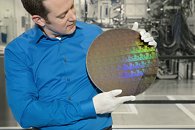

According to the analyst Ming-Chi Kuo, who is a well-known insider in the Apple industry, we can expect the first wave of the Arm-powered Macbook in the next 18 months, precisely in the first half of 2021. Supposedly, the first chips for these new Macs are going to be manufactured on a 5 nm manufacturing process, possibly over at TSMC since Apple had a long-lasting history of manufacturing its chips at TSMC foundries. In the meantime, we can expect to see Apple providing developers with tools to transition their x86-64 software to the new Arm ISA. Without a software ecosystem, the hardware platform is essentially worthless. And Apple knows this. We will see how they plan to play it and will report as soon as there is more information.

According to the analyst Ming-Chi Kuo, who is a well-known insider in the Apple industry, we can expect the first wave of the Arm-powered Macbook in the next 18 months, precisely in the first half of 2021. Supposedly, the first chips for these new Macs are going to be manufactured on a 5 nm manufacturing process, possibly over at TSMC since Apple had a long-lasting history of manufacturing its chips at TSMC foundries. In the meantime, we can expect to see Apple providing developers with tools to transition their x86-64 software to the new Arm ISA. Without a software ecosystem, the hardware platform is essentially worthless. And Apple knows this. We will see how they plan to play it and will report as soon as there is more information.