With the x86 architecture, large hyperscale cloud providers have been experiencing all sorts of troubles, from high power consumption to the high pricing structure of these processors. Companies like Amazon Web Services (AWS) build their processors based on 3rd party instruction set architecture designs. Today, Alibaba, the Chinese giant, has announced the launch of two processors made in-house to serve everything from edge to central server processing. First in line is the RISC-V-based Xuantie series of processors, which can run anything from AliOS, FreeRTOS, RT-Thread, Linux, Android, etc., to other operating systems as well. These processors are open-source, capable of modest processing capabilities, and designed as IPs that anyone can use. You can check them out on T

-Head GitHub repositories here.

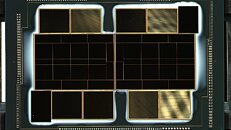

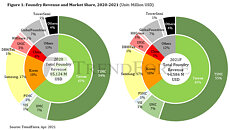

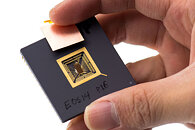

The other thing that Alibaba announced is the development of a 128-core custom processor based on the Arm architecture. Called Yitian 710 server SoC, TSMC manufactures it on the company on 5 nm semiconductor node. So far, Alibaba didn't reveal any details about the SoC and what Arm cores are used. However, this signifies that the company seeks technology independence from outside sources and wants to take it all in-house. With custom RISC-V processors for lower-power tasks and custom Arm server CPUs, the whole infrastructure is covered. It is just a matter of time before Alibaba starts to replace x86 makers in full. However, given the significant number of chips that the company needs, it may not happen at any sooner date.