Samsung Aims to Become Number One Android AP Vendor by Joining Forces with AMD and Arm

Samsung Electronics has reportedly laid out a plan to become the number one Android application processor (AP) vendor in the industry with its plan to join forces with AMD and Arm. The report of Business Korea indicates that Samsung wants to use both company's knowledge and IP to produce the best possible silicon. In early November of last year, Samsung has decided to shut down its division responsible for making custom CPU designs, and to start licensing IP from Arm. Also last year, Samsung has announced a strategic partnership with AMD to use its RDNA graphics processors in smartphones.

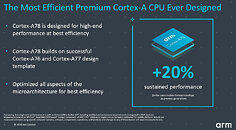

So Samsung plans to license IPs from both companies and just put them in SoC that will be up to the task to deliver the best performance, as the company predicts. The CPU is reportedly going to be based on Arm's Cortex-X custom design that should deliver high-performance Samsung wants. In the past, the company had some problems with the heat-management of its CPUs as they were designed a bit inefficiently. To cover everything, Samsung also plans to increase the number of employees working on a neural processing unit (NPU) and make a good performing NPUs as well, to combine with the rest of IPs.

So Samsung plans to license IPs from both companies and just put them in SoC that will be up to the task to deliver the best performance, as the company predicts. The CPU is reportedly going to be based on Arm's Cortex-X custom design that should deliver high-performance Samsung wants. In the past, the company had some problems with the heat-management of its CPUs as they were designed a bit inefficiently. To cover everything, Samsung also plans to increase the number of employees working on a neural processing unit (NPU) and make a good performing NPUs as well, to combine with the rest of IPs.