Intel Ice Lake-SP Processor Spotted with 36 Cores and 3.6 GHz Base Clock

Today, in the latest GeekBench 5 submission by ASUS, we have discovered something rather interesting. Intel's Ice Lake-SP processors were rumored to arrive with up to 28 cores and 56 threads at maximum, on a single chip. That was due to the 10 nm process used to make these chips, with suspicions that the yield of the node was not good enough to make any higher core count parts. Thanks to the GB5 listing, discovered by Leakbench on Twitter, the Intel Ice Lake-SP CPU engineering sample appeared with an amazing 36 cores with 72 threads. This is supposedly Intel's efforts to try and match the 64 cores and 128 threads of AMD's EPYC "Rome" CPUs, which are winning many server applications due to their performance.

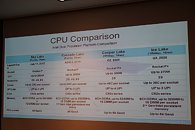

The 36C/72T chip was paired with another similar chip in a 2P dual-socket configuration, which made the total core count rise to 72 cores and 144 threads, running inside of Asustek's Y4R-A1-ASUS-G1 server. The system was reporting a clock frequency of 3.6 GHz base speed, which means that the possible boost clocks could be higher. The CPU features a 1.25 MB level two (L2) cache per core (45 MB in total) and 54 MB of unified level three (L3) cache. That makes this CPU core quite an improvement over the past Cooper Lake generation. We are waiting for more information about these CPUs, and we are going to report on it in the coming time.

The 36C/72T chip was paired with another similar chip in a 2P dual-socket configuration, which made the total core count rise to 72 cores and 144 threads, running inside of Asustek's Y4R-A1-ASUS-G1 server. The system was reporting a clock frequency of 3.6 GHz base speed, which means that the possible boost clocks could be higher. The CPU features a 1.25 MB level two (L2) cache per core (45 MB in total) and 54 MB of unified level three (L3) cache. That makes this CPU core quite an improvement over the past Cooper Lake generation. We are waiting for more information about these CPUs, and we are going to report on it in the coming time.