AMD "Milan-X" Processor Could Use Stacked Dies with X3D Packaging Technology

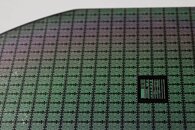

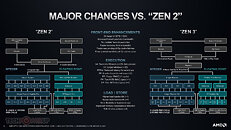

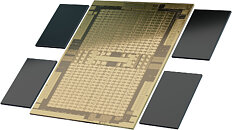

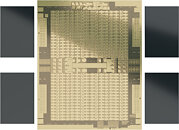

AMD is in a constant process of processor development, and there are always new technologies on the horizon. Back in March of 2020, the company has revealed that it is working on new X3D packaging technology, that integrated both 2.5D and 3D approaches to packing semiconductor dies together as tightly as possible. Today, we are finally getting some more information about the X3D technology, as we have the first codename of the processor that is featuring this advanced packaging technology. According to David Schor, we have learned that AMD is working on a CPU that uses X3D tech with stacked dies, and it is called Milan-X.

The Milan-X CPU is AMD's upcoming product designed for data center usage. The rumors suggest that the CPU is designed for heavy bandwidth and presumably a lot of computing power. According to ExecutableFix, the CPU uses a Genesis-IO die to power the connectivity, which is an IO die from EPYC Zen 3 processors. While this solution is in the works, we don't know the exact launch date of the processor. However, we could hear more about it in AMD's virtual keynote at Computex 2021. For now, take this rumor with a grain of salt.

The Milan-X CPU is AMD's upcoming product designed for data center usage. The rumors suggest that the CPU is designed for heavy bandwidth and presumably a lot of computing power. According to ExecutableFix, the CPU uses a Genesis-IO die to power the connectivity, which is an IO die from EPYC Zen 3 processors. While this solution is in the works, we don't know the exact launch date of the processor. However, we could hear more about it in AMD's virtual keynote at Computex 2021. For now, take this rumor with a grain of salt.