TSMC Accelerates 2 nm Semiconductor Node R&D

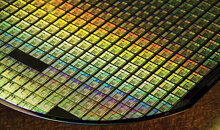

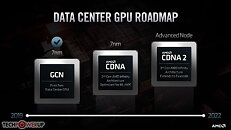

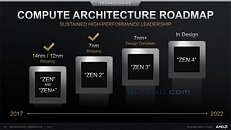

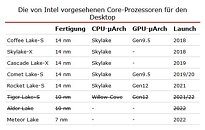

TSMC, the world's leading semiconductor manufacturing company, has reportedly started to accelerate research and development (R&D) of its next-generation 2 nm node. Having just recently announced that they will be starting production of a 5 nm process in Q4 of 2020, TSMC is pumping out nodes very fast and much faster compared to competition like Intel and Samsung. Having an R&D budget of almost 16 billion USD, TSMC seems to be spending the funds very wisely. The 5 nm node is going into volume production this year, and smaller nodes are already being prepared.

The 3 nm node is going into trial production in the first half of 2021, while the mass production is supposed to commence in 2022. As far as the 2 nm node, TSMC has recently purchased more expensive Extreme Ultra-Violet (EUV) lithography machines for the 2 nm node. Due to the high costs of these EUV machines, TSMC's capital spending will not be revisited this year and it should remain in the $16 billion range. As far as a timeline for 2 nm is concerned, we don't know when will TSMC start trial production as the node is still in development phases.

The 3 nm node is going into trial production in the first half of 2021, while the mass production is supposed to commence in 2022. As far as the 2 nm node, TSMC has recently purchased more expensive Extreme Ultra-Violet (EUV) lithography machines for the 2 nm node. Due to the high costs of these EUV machines, TSMC's capital spending will not be revisited this year and it should remain in the $16 billion range. As far as a timeline for 2 nm is concerned, we don't know when will TSMC start trial production as the node is still in development phases.