JNTC Unveils Next-Generation Glass Substrate for Semiconductors

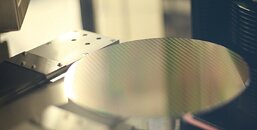

JNTC Co., Ltd., a leading advanced materials company, hosted a product launch on June 30 at the Korea Exchange Conference Hall, unveiling its new Through-Glass-Via (TGV) glass substrate under the theme Carving Semiconductors into Glass, the Dream Material.' The event drew more than 200 attendees, including journalists and investors. CEO Andrew Cho introduced the proprietary TGV glass substrate as a breakthrough solution to the limitations of plastic-based substrates. Designed for AI and high-performance computing applications, the substrate offers excellent flatness and thermal stability, which help reduce warpage and heat generation under high-speed processing.

JNTC completed its domestic production line in June and expects to begin full-scale manufacturing in August, following test runs in July. Unlike competitors, JNTC built and engineered most of its core production equipment in-house, enabling cost efficiency and full process independence. This approach cut initial investment costs to about one-fifth of the industry average.

JNTC completed its domestic production line in June and expects to begin full-scale manufacturing in August, following test runs in July. Unlike competitors, JNTC built and engineered most of its core production equipment in-house, enabling cost efficiency and full process independence. This approach cut initial investment costs to about one-fifth of the industry average.