Friday, November 9th 2012

Future Itanium and Xeon Processors Socket-Intercompatible

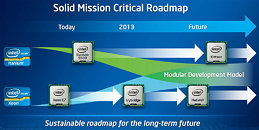

In what could be the very first time two different machine architectures share a platform, future versions of Intel's Xeon and Itanium processors could be socket-compatible. Intel Itanium is based on the Itanium64 (IA64) machine architecture, while Xeon is x86-64 based. Intel plans to implement its common platform strategy with the next generation models of the two, that's "Kittson" Itanium, and "Haswell" Xeon.

This level of convergence could make it easier for companies to deploy select amounts of Itanium and Xeon processors in their data-centers, to suit specific tasks, and save money on buying common platforms for both. Itanium processors are typically preferred for in mission-critical environments, where there's close to zero margin for error (think military, medical, and space-exploration); while Xeon is good at handling heavy serial processing loads (think servers, database management, cloud). Introduction of the converged platform is expected in the 2013-2015 time range, using Xeon "Haswell" launch as a point of reference.

Source:

X-bit Labs

This level of convergence could make it easier for companies to deploy select amounts of Itanium and Xeon processors in their data-centers, to suit specific tasks, and save money on buying common platforms for both. Itanium processors are typically preferred for in mission-critical environments, where there's close to zero margin for error (think military, medical, and space-exploration); while Xeon is good at handling heavy serial processing loads (think servers, database management, cloud). Introduction of the converged platform is expected in the 2013-2015 time range, using Xeon "Haswell" launch as a point of reference.

44 Comments on Future Itanium and Xeon Processors Socket-Intercompatible

If I (as a computer engineer) mean to program a CPU to calculate 1 + 1 but I accidentally program it to calculate 1 + 2, that's a logic error. The CPU will NEVER be able to correct it (unless it's some kind of advanced AI that can predict what I MEANT to program :rolleyes: ) and will give an answer of 3 regardless.

If however I program it correctly to calculate 1 + 1 and it gives an answer of say 405,353, an insertion or deletion error occurred somewhere in memory or cache. This kind of error can be detected and corrected by the CPU or O/S through checksums, parity bits and coding. That PDF you linked to just states that the Itanium has a number of ECC levels to ensure that even entire blocks of insertion/deletion errors can be corrected in memory, cache, bus etc. Regardless, it will still never be able to correct a logic error.

What HP-UX does is software ECC on top of the already significant hardware ECC present in the Itanium. So it will use additional parity information to correct errors that were left uncorrected by the CPU.

For mission critical use though, a crash might amount to millions of dollars in lost revenue. Also, hardware such as memory and cache has reached pretty decent reliability figures so the advanced ECC features found in Itanium at CPU and memory level is usually not needed for desktop applications.

Error detection IS used in other desktop systems though, ex. Network Ethernet frames are sent with parity information to ensure the packet arrives without errors. I believe the PCI-Express standard also utilizes some primitive ECC features in normal operation - at least to detect errors if not correct them.

There is a reason they are still fourth. en.wikipedia.org/wiki/POWER7

www.wired.com/wiredenterprise/2012/02/hp-itanium/

HP is about the only ones left supporting Itanium, and 700 million is almost a fourth of the whole Itanium sales from Intel.

peopleprocesstech.com/2012/06/05/why-the-hp-superdome-is-as-dead-as-a-dodo/

Westmere does most of the same things. Bulldozer supports ECC memory, and its own caches are ECC protected.