Monday, November 25th 2019

AMD "Zen 3" Microarchitecture Could Post Significant Performance Gains

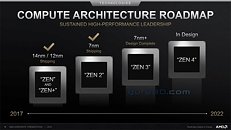

At its recent SC19 talk, AMD touched upon its upcoming "Zen 3" CPU microarchitecture. Designed for the 7 nm EUV silicon fabrication process that significantly increases transistor densities, "Zen 3" could post performance gains "right in line with what you would expect from an entirely new architecture," states AMD, referring to the roughly 15 percent IPC gains that were expected of "Zen 2" prior to its launch. "Zen 2" IPC ended up slightly over 15 percent higher than that of the original "Zen" microarchitecture. AMD's SC19 comments need not be a guidance on the IPC itself, but rather performance gains of end-products versus their predecessors.

The 7 nm EUV process, with its 20 percent transistor-density increase could give AMD designers significant headroom to increase clock speeds to meet the company's generational performance improvement targets. Another direction in which "Zen 3" could go is utilizing the additional transistor density to bolster its core components to support demanding instruction-sets such as AVX-512. The company's microarchitecture is also missing something analogous to Intel's DLBoost, an instruction-set that leverages fixed-function hardware to accelerate AI-DNN building and training. Even VIA announced an x86 microarchitecture with AI hardware and AVX-512 support. In either case, the design of "Zen 3" is complete. We'll have to wait until 2020 to find out how fast "Zen 3" is, and the route taken to get there.

Source:

Guru3D

The 7 nm EUV process, with its 20 percent transistor-density increase could give AMD designers significant headroom to increase clock speeds to meet the company's generational performance improvement targets. Another direction in which "Zen 3" could go is utilizing the additional transistor density to bolster its core components to support demanding instruction-sets such as AVX-512. The company's microarchitecture is also missing something analogous to Intel's DLBoost, an instruction-set that leverages fixed-function hardware to accelerate AI-DNN building and training. Even VIA announced an x86 microarchitecture with AI hardware and AVX-512 support. In either case, the design of "Zen 3" is complete. We'll have to wait until 2020 to find out how fast "Zen 3" is, and the route taken to get there.

38 Comments on AMD "Zen 3" Microarchitecture Could Post Significant Performance Gains

I'm very pro AVX-512 :)"Desktop software"? As opposed to what? :PNope. Software is compiled for ISA, but it's written using libraries.

Libraries can impact compilation as well.

Intel MKL is usually faster than alternatives (like OpenBLAS) on the same CPUs - utilizing the same instructions. It produces different low-level code.

But I do still wonder if too rapid iterations leaves development time for necessary improvements in the long run.Mobile stuff in general is ARM, embedded software could be ARM, MIPS, etc.Your claim was that is written for (Intel's) APIs. While both Intel and AMD does provide some libraries, software in general don't rely on these. And software in general is not more "Intel optimized", if that's what you're implying.Really? Dynamically linked libraries is not compiled into the software you know ;)

Zen3 will be a minor arch tweak but still TSMC 7nm so don't expect huge improvements (5-10% maybe?) and I'm not sure that's worth waiting 6-9 months for. Hell, the 3950X was 5 months later than the rest of the Zen2 chips, so the 4950X could be a mid-2021 product with the 4900X holding the line for a while like the 3900X had to.

from Merriam-Webster.com

Sorry, could help it. Live and learn, right?:rockout:

:lovetpu: