Monday, September 22nd 2008

Phenom X4, X3 45nm Lineup for H1 2009 Explained

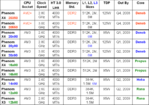

AMD would be releasing its first desktop processors based on the 45nm silicon fabrication process, based on the newer Deneb core. The company is said to have made several tweaks to the original K10 design and equipped the core with 300% the amount of L3 cache as its 65nm Agena parts. The only thing got us wondering was what would be its nomenclature like? Well, be surprised to know that after Phenom X4 9000 series, the company plans to continue the numbering with a 5-digit model number scheme with x1000 unit deviations between models. A rather confusing naming scheme, as suggested by the chart provided, seems to have been adopted.

It is now clear, that there will be two distinct kinds of Phenom X4 45nm chips: those which continue support for DDR2 memory on the existing AM2/AM2+ sockets, and those which are exclusive to the AM3 socket and feature support for DDR3 memory, DDR3 1333MHz at that. The processors would feature dual 64-bit memory controllers, which could be ganged for a single 128-bit wide memory interface, or un-ganged to step up multi-tasking efficiency.The first two Phenom parts out are, Phenom X4 20350, clocked at 2.80 GHz, and a higher model, Phenom X4 20550, clocked at 3.00 GHz. Both these parts are DDR2 compatible which extends the life of current AM2/AM2+ platform. Both have rated TDP of 125W. This is an improvement over the 65nm parts, which had a third of the amount of L3 cache and the 2.60 part being rated at 140W.

Next up, is a fleet of AM3 socket processors that use DDR3-1333 as the memory standard. Their nomenclature starts from the 16xxx range, extending up to 20xxx depending on the clock speed. It can be seen that the parts with a full 8 MB cache (4x 512 KB L2 + 6 MB L3) feature a 20xxx number, while those based on the Propus core which lack L3 caches, feature a total of 2 MB cache (4x 512 KB), have 16xxx series number depending on their clock speeds. Interestingly, there's a part with 3 MB cache featured. We're not sure how the math works out. Finally, 45nm Phenom X3 parts are listed, with their two kinds of cores depending on the presence of L3 caches. They use 14xxx for those with the L3 cache (Heka core), and 12xxx for those without them (Rana core). As you can see, the model numbers are now a complete deviation from the PRN system AMD used only an year ago with its Athlon 64 X2 chips. Also mentioned are their tentative release dates. AM2+ Deneb chips are just around the corner.

Source:

Expreview

It is now clear, that there will be two distinct kinds of Phenom X4 45nm chips: those which continue support for DDR2 memory on the existing AM2/AM2+ sockets, and those which are exclusive to the AM3 socket and feature support for DDR3 memory, DDR3 1333MHz at that. The processors would feature dual 64-bit memory controllers, which could be ganged for a single 128-bit wide memory interface, or un-ganged to step up multi-tasking efficiency.The first two Phenom parts out are, Phenom X4 20350, clocked at 2.80 GHz, and a higher model, Phenom X4 20550, clocked at 3.00 GHz. Both these parts are DDR2 compatible which extends the life of current AM2/AM2+ platform. Both have rated TDP of 125W. This is an improvement over the 65nm parts, which had a third of the amount of L3 cache and the 2.60 part being rated at 140W.

Next up, is a fleet of AM3 socket processors that use DDR3-1333 as the memory standard. Their nomenclature starts from the 16xxx range, extending up to 20xxx depending on the clock speed. It can be seen that the parts with a full 8 MB cache (4x 512 KB L2 + 6 MB L3) feature a 20xxx number, while those based on the Propus core which lack L3 caches, feature a total of 2 MB cache (4x 512 KB), have 16xxx series number depending on their clock speeds. Interestingly, there's a part with 3 MB cache featured. We're not sure how the math works out. Finally, 45nm Phenom X3 parts are listed, with their two kinds of cores depending on the presence of L3 caches. They use 14xxx for those with the L3 cache (Heka core), and 12xxx for those without them (Rana core). As you can see, the model numbers are now a complete deviation from the PRN system AMD used only an year ago with its Athlon 64 X2 chips. Also mentioned are their tentative release dates. AM2+ Deneb chips are just around the corner.

61 Comments on Phenom X4, X3 45nm Lineup for H1 2009 Explained

It is not Hypocrytical to say AMD is doing it for different reasons than Intel. AMD NEEDS to do it because their performance is sub-par, they are adding the cache to help improve performance. Likely Intel is doing the same, adding cache is an easy way to help performance.

The big difference is that Intel doesn't need to add it, and didn't add nearly as much as AMD. AMD has doubled the cache on their processors, Intel added 50%. And I wasn't totally accurate in saying that the added cache on Intel's processors didn't help any, it does help in a lot of multi-media area actually.

AMD is jacking up the amount of cache to try and make up for the sub-par performance of the K10/Phenom architecture, just like Intel did with Netburst. Intel isn't doing the same with the Core 2 because their performance is Sub-Par. I'm not saying either side didn't add cache, and I'm not saying either side didn't add cache to improve performance. I'm saying that AMD is doing it to an insane level because it is their only option to improve performance at this point.

Oh, and there are no posts in that thread that back your statement up. Unless you call a few posts showing the Phenom managing to equal or surpase the Core 2 at he same clocks in a total of 4 out of 35 tests. Again, maybe if it was a little closer to 50/50 I would be more inclined to agree with your statement.

At this point, anyone that would make the statement that Phenom/K10 perform on par with Core 2 is either completely ignorant or a fanboy. Which are you?

Edit: Of course you are more than welcome to post some benchs that actually back your statement up and prove me wrong, if you can.You can't just look at clock speeds as a universal thing. Clocking netburst processors over 3GHz wasn't insane, in fact the netburst architecture was designed with high clock speeds in mind. You have to look at the clock speeds in context of the architecture. Ever since the Athlon days, an insane clock on an AMD was way lower than an insane clock on a P4. Over 3GHz on an Athlon XP was completely insane, but 3GHz is nothing on a P4. It all has to do with context of the architecture. 3GHz on a Phenom is insane, hell a 3GHz overclock on a Phenom is damn good right now, so releasing a stock processor that is clocked at the speed that most overclockers consider a good overclock is insane.

to the added cache, i think there were some tests showing that the actual phenom architecture doesn't profit that much from added cache and now i think AMD is either adding a huge amount of cache, because they didn't change that much and thats the only way to compensate or the improvements really profit from the cache ... either way i'm eagerly waiting for the 45nm phenoms to show up ... yikes, it sound really confusing :o :banghead: :rockout:

"Up to par" does not have to mean "faster than" -- it means an acceptable level of performance in relation to something else. And I'm still not fully convinced that any benchmarks that show Intel chips with huge leads aren't because of some Intel-only instruction set that, of course, AMD is not going to be able to match.

Oh, and now we have gone from "equal" to "up to par", your argument just keeps getting worse. No one said "up to par", you are just trying to change the argument to help your side out. You and I both said "on par" which means equal to, look it up.

Oh, so now anything that Intel wins, it has to be because of some instruction set that AMD could never match. It could't be because the processor are just better, could it? And even if it was because of an instruction set, it doesn't matter, Intel's processors still outperformed AMD's. The architecture is just better.

Intel

AMD

Intel

AMD

Intel

AMD

Intel

AMD

...

..

.

getting the pattern here? :D