Samsung Launches Sixth Generation 3D V-NAND SSDs

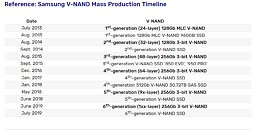

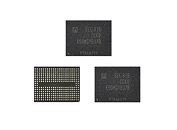

Samsung Electronics, the world leader in advanced memory technology, today announced that it has begun mass producing 250-gigabyte (GB) SATA solid state drive (SSD) that integrates the company's sixth-generation (1xx-layer) 256-gigabit (Gb) three-bit V-NAND for global PC OEMs. By launching a new generation of V-NAND in just 13 months, Samsung has reduced the mass production cycle by four months while securing the industry's highest performance, power efficiency and manufacturing productivity.

"By bringing cutting-edge 3D memory technology to volume production, we are able to introduce timely memory lineups that significantly raise the bar for speed and power efficiency," said Kye Hyun Kyung, executive vice president of Solution Product & Development at Samsung Electronics. "With faster development cycles for next-generation V-NAND products, we plan to rapidly expand the markets for our high-speed, high-capacity 512 Gb V-NAND-based solutions."

"By bringing cutting-edge 3D memory technology to volume production, we are able to introduce timely memory lineups that significantly raise the bar for speed and power efficiency," said Kye Hyun Kyung, executive vice president of Solution Product & Development at Samsung Electronics. "With faster development cycles for next-generation V-NAND products, we plan to rapidly expand the markets for our high-speed, high-capacity 512 Gb V-NAND-based solutions."