Vicor 1200A Hydra ChiP-set Enables Higher Performance AI Accelerator Cards

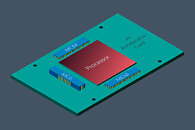

Vicor Corporation today announced a ChiP-set for high performance GPU, CPU, and ASIC ("XPU") processors powered directly from 48 V. A driver, MCD4609, and a pair of MCM4609 current multiplier modules supply up to 650 A continuous and 1200 A peak. Owing to their small footprint and low profile (45.7 x 8.6 x 3.2 mm), current multipliers are placed close to the processor enabling reduced power distribution network (PDN) losses and higher power system efficiency. Powering GPU and OCP Accelerator Module (OAM) Artificial Intelligent (AI) cards, the 4609 ChiP-set is in mass production and available to new customers on the Vicor Hydra II evaluation board.

The 4609 ChiP-set adds to the Vicor Power-on-Package portfolio of Lateral Power Delivery (LPD) solutions. To raise the bar of current capability above the limits of LPD, Vicor's pioneering Vertical Power Delivery (VPD) will soon enable much higher current density. The VPD system delivers current from power converters vertically stacked under a processor through a capacitor network geared to a processor-specific pin-map. A GCM ("Gearbox Current Multiplier") is a specialized VPD embodiment incorporating a gearbox capacitor network as a layer in the vertical stack. By supplying current directly under the processor and eliminating PDN losses, GCMs will soon facilitate current densities reaching up to 2 A per mm².

The 4609 ChiP-set adds to the Vicor Power-on-Package portfolio of Lateral Power Delivery (LPD) solutions. To raise the bar of current capability above the limits of LPD, Vicor's pioneering Vertical Power Delivery (VPD) will soon enable much higher current density. The VPD system delivers current from power converters vertically stacked under a processor through a capacitor network geared to a processor-specific pin-map. A GCM ("Gearbox Current Multiplier") is a specialized VPD embodiment incorporating a gearbox capacitor network as a layer in the vertical stack. By supplying current directly under the processor and eliminating PDN losses, GCMs will soon facilitate current densities reaching up to 2 A per mm².