TSMC and ARM Tape-Out First ARM Cortex-A57 Processor on 16 nm FinFET Technology

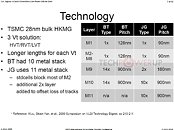

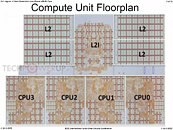

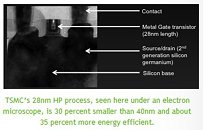

TSMC and ARM today announced the first tape-out of an ARM Cortex-A57 processor on FinFET process technology. The Cortex-A57 processor is ARM's highest performing processor, designed to further extend the capabilities of future mobile and enterprise computing, including compute intensive applications such as high-end computer, tablet and server products. This is the first milestone in the collaboration between ARM and TSMC to jointly optimize the 64-bit ARMv8 processor series on TSMC FinFET process technologies. The two companies cooperated in the implementation from RTL to tape-out in six months using ARM Artisan physical IP, TSMC memory macros, and EDA technologies enabled by TSMC's Open Innovation Platform (OIP) design ecosystem.

ARM and TSMC's collaboration produces optimized, power-efficient Cortex-A57 processors and libraries to support early customer implementations on 16 nm FinFET for high-performance, ARM technology-based SoCs.

ARM and TSMC's collaboration produces optimized, power-efficient Cortex-A57 processors and libraries to support early customer implementations on 16 nm FinFET for high-performance, ARM technology-based SoCs.