Tuesday, February 9th 2010

AMD to Sample 32 nm Processors Within H1 2010

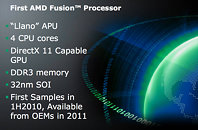

AMD, in its presentation at the International Solid State Circuits Conference (ISSCC) 2010, presented its plan to build its much talked about 'Fusion' processor platform, codenamed Llano, central to which, is the Accelerated Processing Unit (APU). AMD's APU is expected to be the first design to embed a multi-core x86 CPU and a GPU onto a single die. This design goes a notch ahead of Intel's recently released 'Clarkdale' processor, where Intel strapped a 32 nm dual-core CPU die and a 45 nm northbridge die with integrated graphics, onto an MCM (multi chip module) package. Llano is also expected to feature four processing cores, along with other design innovations.

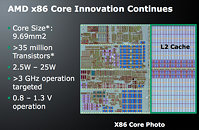

Some of the most notable announcements in AMD's presentation is that the company will begin sampling the chip to its industry partners within the first half of 2010. The Llano die will be build on a 32 nm High-K Metal Gate process. On this process, each x86 core will be as small as 9.69 mm². Other important components on the Llano die are a DDR3 memory controller, on-die northbridge, and a DirectX 11 compliant graphics core derived from the Evergreen family of GPUs. The x86 cores are expected to run at speeds of over 3 GHz. Each core has 1 MB of dedicated L2 cache, taking the total chip cache size to 4 MB.AMD has also embraced some new power management technologies, including power gating. Power gating is a feature that allows the system to power down some x86 core to push their power draw to near-zero. This reduces the chip's overall power draw better, which also allows active cores to be powered up. Similar to Intel's Turbo Boost technology. The power aware clock grid design reduces power consumption by cutting down on clock distribution across the chip.

With the APU, AMD thinks it has the right product for tomorrow's market, a chip which packs a large chunk of the motherboard's silicon, while not compromising on the features due to space constraints within the package. There's room made for four processing cores, and an Evergreen-derived DirectX 11 compliant GPU. If implemented well enough on the software side, AMD believes it can deliver one chip that handles both serial processing workloads (by the x86 cores), and highly parallel workloads (by the stream processors). Market availability of the chip isn't definitively known, but we expect it to be out early next year, or late this year.

Some of the most notable announcements in AMD's presentation is that the company will begin sampling the chip to its industry partners within the first half of 2010. The Llano die will be build on a 32 nm High-K Metal Gate process. On this process, each x86 core will be as small as 9.69 mm². Other important components on the Llano die are a DDR3 memory controller, on-die northbridge, and a DirectX 11 compliant graphics core derived from the Evergreen family of GPUs. The x86 cores are expected to run at speeds of over 3 GHz. Each core has 1 MB of dedicated L2 cache, taking the total chip cache size to 4 MB.AMD has also embraced some new power management technologies, including power gating. Power gating is a feature that allows the system to power down some x86 core to push their power draw to near-zero. This reduces the chip's overall power draw better, which also allows active cores to be powered up. Similar to Intel's Turbo Boost technology. The power aware clock grid design reduces power consumption by cutting down on clock distribution across the chip.

With the APU, AMD thinks it has the right product for tomorrow's market, a chip which packs a large chunk of the motherboard's silicon, while not compromising on the features due to space constraints within the package. There's room made for four processing cores, and an Evergreen-derived DirectX 11 compliant GPU. If implemented well enough on the software side, AMD believes it can deliver one chip that handles both serial processing workloads (by the x86 cores), and highly parallel workloads (by the stream processors). Market availability of the chip isn't definitively known, but we expect it to be out early next year, or late this year.

46 Comments on AMD to Sample 32 nm Processors Within H1 2010

Im wondering if the GPU will be able to handle anything recent at a acceptable rez. We will prob see a 5400 variant(80 shaders) in there, although a 5570/50 (400 shaders w/ddr3) would be a HUGE advancement. They may even go in between these two shader count wise; but this is just one mans speculation/hope!!

I'm tempted to follow the heat on this stuff and get some when it hits the market.

:}

One of the big innovations to look forward to IMO, the other being OLED screens, as opposed to just simple ever increasing raw processing power.:)

Looks good.

But yes if they play there cards right, we may be seeing these kinds of chips smoke in gaming,

I hope they work it out and crush big blue in the notebook/netbook department :nutkick:

if thats not the case, AMD will be in the same spot as Intel is with its integrated gpu, graphicscore just for the graphic but not for apps

Yes boys and girls the future is now, not for true gamers but for everything else.