Wednesday, July 27th 2011

Intel Aims at 10 nm Processors by 2018

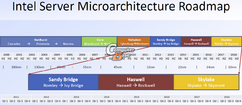

It's not just host nations of the Olympics that are decided almost decades in advance, but also Intel's silicon names and the fab process they're going to be built on. Intel has its plan for the greater part of this decade already charted out, well beyond the upcoming Ivy Bridge architecture. Intel follows the "tick-tock" product cycle, where every micro-architecture gets to be built on two succeeding fab processes, and every fab process getting to have two succeeding micro-architectures built on it, in succession. Westmere is an optical shrink of the Nehalem architecture, it was a "tick" for the 32 nm process, Sandy Bridge is its "tock", and a new architecture. Ivy Bridge is essentially an optical shrink of Sandy Bridge, it is the "tick" for 22 nm process.

Ivy Bridge will make its entry through the LGA1155 platform in 2012, it will make up the 2012 Core processor family. Haswell is the next-generation architecture that succeeds Sandy Bridge and IvyBridge, it will be built on the 22 nm process, and is expected to arrive in 2013. Roswell is its optical shrink to 14 nm, slated for 2014. Looking deep into the decade, there's Skylake architecture, that will span across 14 nm and 10 nm processes with Skymont. This model ensures that Intel has to upgrade its fabs every 2 or so years, an entirely new micro-architecture every 2 or so years as well, while providing optical shrinks every alternating year. Optical shrinks introduce new features, increased caches, and allow higher clock speeds. 10 nm for processors by 2018 sounds realistic looking at the advancement of NAND flash technologies that are pushing the boundaries of fab process development. NAND flash is much less complex than processor development, and hence serve as good precursors to a new process.

Source:

ComputerBase.de

Ivy Bridge will make its entry through the LGA1155 platform in 2012, it will make up the 2012 Core processor family. Haswell is the next-generation architecture that succeeds Sandy Bridge and IvyBridge, it will be built on the 22 nm process, and is expected to arrive in 2013. Roswell is its optical shrink to 14 nm, slated for 2014. Looking deep into the decade, there's Skylake architecture, that will span across 14 nm and 10 nm processes with Skymont. This model ensures that Intel has to upgrade its fabs every 2 or so years, an entirely new micro-architecture every 2 or so years as well, while providing optical shrinks every alternating year. Optical shrinks introduce new features, increased caches, and allow higher clock speeds. 10 nm for processors by 2018 sounds realistic looking at the advancement of NAND flash technologies that are pushing the boundaries of fab process development. NAND flash is much less complex than processor development, and hence serve as good precursors to a new process.

64 Comments on Intel Aims at 10 nm Processors by 2018

10nm will be a challenge to made as they all(not only intel) already have problems with 22nm....

hot electron effect

impact ionization

velocity saturation

drain induced barrier lowering

surface scattering

punchthrough

sub-threshold conduction

skylake-->skymont-->skynet

It was actually a Q1 2011 release.

Does that mean that the whole graph is ahead three quarters?

Also I wonder if it will run Crysis......Sorry I know thats 7 years early but we here on TPU are always cutting edge.They got 7 years. Thats a several lifetimes in the tech world.

Graphene does have a much smaller lattice spacing iirc and I've seen claims of 2 layers of graphene being able to create a Cassimir Effect, so what about some science fiction and dreaming of autopowered chips (zero point energy)??!! :rockout:

Using new materials like graphene may provide scaling beyond the capabilities of silicon, but still dynamic power consumption will be a problem.Adiabatic logic is a solution

Even if the traces in the CPU are 1nm they can make the insulator around and beside it 20nm if they need to, it just creates more heat as the electrical path is longer, and more latency from the same issue. However their 3D transistor should help with trace length, and thus electrical needs, and a shorter path also reduces the capacitive roll off charge. All that adds up to lower electrical needs, faster processing physically in the chip, and lower TDP.

The graphics card makers have already fought with memory management, I see this as being a plus for AMD, their dedicated cards have already taught them about the best way to perform on die termination, signaling, voltages, and path length. Intel had a bit of a issue with that on some chips, the termination voltage was burning out processors. They have probably already started work on the same issue as they make smaller and smaller traces on the CPU.