Thursday, April 30th 2015

AMD Zen-based 8-core Desktop CPU Arrives in 2016, on Socket FM3

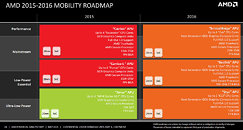

In what is a confirmation that AMD has killed socket AM3+ and its 3-chip platform, a leaked slide that's part of a larger press-deck addressing investors, tells us that the company is planning to launch a high-performance desktop processor targeting enthusiasts, based on its next-generation "Zen" architecture, in 2016. Our older articles detail the Zen CPU core design, and the way in which AMD will build multi-core CPUs with it. This processor will be codenamed "Summit Ridge," and will be a CPU, and not an APU as previously reported. In AMD-speak, what sets a CPU apart from an APU is its lack of integrated graphics.

AMD "Summit Ridge" will be an 8-core CPU built on the 14 nanometer silicon fab process. It will feature eight "Zen" cores, with 512 KB of L2 cache per core, 16 MB of L3 cache, with 8 MB shared between two sets of four cores, each; a dual-channel integrated memory controller that likely supports both DDR3 and DDR4 memory types; and an integrated PCI-Express gen 3.0 root complex, with a total of 22 lanes. We can deduce this from the fact that "Summit Ridge" will be built in the same upcoming socket FM3 package, which the company's "Bristol Ridge" Zen-based APU will be built on. "Summit Ridge" will hence be more competitive with Intel's 6th generation Core "Skylake" processors, such as the i7-6700K and i5-6600K, than the company's "Broadwell-E" HEDT platform.The mainstream APU based on Zen, codenamed "Bristol Ridge," features four Zen cores, 512 KB of L2 cache, 8 MB of shared L3 cache, an integrated GPU based on AMD's "Greenland" class stream processors, and a similar uncore loadout as "Summit Ridge."

AMD "Summit Ridge" will be an 8-core CPU built on the 14 nanometer silicon fab process. It will feature eight "Zen" cores, with 512 KB of L2 cache per core, 16 MB of L3 cache, with 8 MB shared between two sets of four cores, each; a dual-channel integrated memory controller that likely supports both DDR3 and DDR4 memory types; and an integrated PCI-Express gen 3.0 root complex, with a total of 22 lanes. We can deduce this from the fact that "Summit Ridge" will be built in the same upcoming socket FM3 package, which the company's "Bristol Ridge" Zen-based APU will be built on. "Summit Ridge" will hence be more competitive with Intel's 6th generation Core "Skylake" processors, such as the i7-6700K and i5-6600K, than the company's "Broadwell-E" HEDT platform.The mainstream APU based on Zen, codenamed "Bristol Ridge," features four Zen cores, 512 KB of L2 cache, 8 MB of shared L3 cache, an integrated GPU based on AMD's "Greenland" class stream processors, and a similar uncore loadout as "Summit Ridge."

73 Comments on AMD Zen-based 8-core Desktop CPU Arrives in 2016, on Socket FM3

TDP is more power consumed and doesn't factor in how well the chip can be cooled. (TIM/solder under the heatspreader, for one example).I'm a bit incorrect. I'll just refer to Wikipedia instead.PCI-e has a bit of latency to it, I believe. Not sure if this is still the case for PCI-e 3.0 though.2) Extra pins. You can have extra unused pins for Bristol and have Summit use those extra pins to connect the southbridge through HT or some other interface. Seeing as how Bristol is a SoC and Summit is not, this seems quite clear to me that these CPUs will not be interchangeable on the same board.

EDIT:

And I'm sure enthusiast board will do both while cheaper boards will be more specific aka..A58, A75, A88X

If they're not interchangeable on the same board, then why do they use the same socket if the pinning is going to be different? That's my point. You already have all the wasted pins from not having a iGPU. With that said, I have an expectation that FM3 won't be an SoC socket like AM1 is. Consider that with AM1, that all the boards are the same because all the CPUs have the same SB hardware on the CPU. Plus, in a tower I see little benefit for using an SoC unless you're trying to cram everything on a very small motherboard.

So while I understand what you're saying, from a design perspective, it doesn't really make much sense. It's a lot of work to support both so I doubt it will.

I guess it's possible...

I've always liked AMD and I hope they bounce back.

The pinning does not need to be different, just certain pins (for the I/O) are not used on a Summit Ridge 1090fx board or are used to connect to the PCH or Southbridge. While on the Bristol Ridge board these same pins are used to connect to the I/O ports. This is not that far fetched. Depending on the CPU the pins have different purposes and are wired differently. Instead of the socket having a fixed pin wiring, it's the CPU (Summit or Bristol, 1090fx or 90x) that determines they're use. This would explain how Styx (ARM K12) and Basilisk (x86) use the same socket.The pipeline determines the clock speed. Short ones have a lower clock speed (fewer calculations per second) while longer ones have higher clock speeds. Long pipelines are not bad as long as you don't stall a core which has been one of the problems with the Bulldozer uarch. The scheduler (from what I've read) can't keep the cores busy so you end up wasting power. If you have a branch prediction miss, it just makes the whole thing worse because the core has to wait for the correct information to be fetched.

Bulldozer was designed by a computer. Then every release after that has just been optimizing to fix how in-efficient the computer made the architecture.

So yea, any thing is possible.

Of course, that's my ideal scenario, but while just an ideal, it is definitely possible that AMD took a bit of time ignoring the general user, all the while actually being more focused, but in a different direction than most might have imagined.

More likely to be FM4 at this stage and low power.

So with that said:

If FM4 is to 1150, then AM4 is to 2011-3.

I say this because if "Xen" is claimed to have a huge number of PCI-E lanes on chip, then I suspect that AM4 will have a very different pinning than we've seen in the past which wouldn't jive nicely with how APUs have had a limited number of PCI-E lanes (22 on FM4 coming up I think). The simple point really is that this is AMD (like Intel) making a distinction between the consumer products and the high-end/server market products. They've really just tuned the lineup with the market in my opinion. More pins = more traces = more money and there is no need to make a mainstream platform expensive if the company is considering their bottom line.

It really comes down to market segmentation. Generally speaking, consumers will be happy with an iGPU and fast cores... and generally speaking, servers and workstations will require either discrete graphics or none at all (minus something super low power and weak) and more cores. But either way, Xen (if half decent,) will find its way into both markets like Bulldozer did. I think that's a given.