Thursday, February 16th 2017

AMD Ryzen Die Shot and New Architecture Details Revealed at ISSCC

At the International Solid-State Circuits Conference held earlier this month, some solid information has come to surface on a subject near and dear to many enthusiast hearts right now: AMD's upcoming Ryzen CPU line.

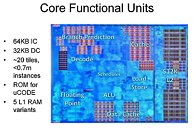

As far as credibility, the information comes in fairly convincing form. AMD's claims are backed with die shots of actual AMD Ryzen cores and further supported by more shots of their CCX (core complex) modules. From these shots, we can guess at several things, and further more see evidence for several of their claims.To get to the meat of the matter, let's start with a die shot of a single AMD Ryzen core.The main thing to notice here is of course the fact that each core has only one integer and FPU section, rather than splitting an FPU between two integer units. This represents a major design departure from earlier designs by AMD such as Bulldozer, Piledriver, etc, but is not entirely a surprise as Ryzen has been known (or at the very least, strongly suspected) to utilize such a config for quite some time now. This represents part of AMD's overall attempt to improve IPC by moving from a CMT (clustered multi-threading) model to a SMT (simultaneous multi-threading) based model, essentially trading two integer sections per core for one larger, better performing one. This will certainly go a long way towards raising single threaded performance and IPC.

All of that was already pretty much known, however. Of much more interest is the little section in the upper right labeled "Branch Prediction". AMD labels this as a "Neural Net Prediction" system, but in actual CPU-terms, it is a really fancy version of something known as a branch predictor. A branch predictor's job is to decide what a branch in the code will do before it actually happens, so the rest of the CPU can get ready for that reality. If it's wrong (and sometimes it is), the rest of the CPU has to spend time cleaning up after its missed prediction. A good branch predictor is not often wrong, though, and saves far more time than it looses by guessing correctly more often than not the outcome of the code path. AMD is essentially claiming that its branch predictor is much improved over previous iterations, and that its learning and training process for selection of outcomes is much more intelligent. Hence the name "Neural Net Prediction."

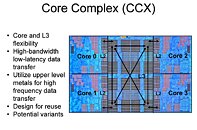

Moving on, let's take a look at a CCX (Core Complex, essentially a quad core module):AMD's main statement about the CCX module is that it is flexible, and allows for several adjustments to be made in the future with regards to L3 cache and core configuration. I would assume this is strong evidence that AMD has plans for Ryzen well beyond the initial "Summit Ridge" line of processors, if one were to be in the guessing game. Furthermore, AMD emphasizes the simplicity of their design. While it is true that Intel's 14nm process is a little more dense than AMD's (smaller), AMD says it has more than made up for this loss with a simpler, more efficient design that saves die space over Intel's present architecture. As such, AMD is confident it is finally on a "node parity" with Intel, something that we have not seen in quite a while, and should have a good many enthusiasts drooling at the very thought.

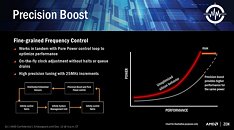

The final bit of AMD's presentation centered around a tech AMD has labeled "Precision Boost," which could be one of the most interesting slides of all.Precision boost appears to be a form of fine grained clock control for the processor, and will likely be used to enable energy savings and perhaps (in the case of XFR) enable a sort of automatic overclocking. Precision boost works hand in hand with AMD's monitoring tech, Pure Power, and clocks a CPU based on its "health and workload." It does this in fine grained 25 MHz increments that AMD says happen without "halts or queue drains." Real world performance of course has yet to be seen, but anything that saves energy or enables extra performance for the average user without delving too deep into overclocking is of course a welcome sight.

All in all, although a lot of this was suspected in the past, to see die shots support the claims and to have actual supportive statements from AMD itself, is always an encouraging thing.Source: PC Watch

Source:

HotHardware

As far as credibility, the information comes in fairly convincing form. AMD's claims are backed with die shots of actual AMD Ryzen cores and further supported by more shots of their CCX (core complex) modules. From these shots, we can guess at several things, and further more see evidence for several of their claims.To get to the meat of the matter, let's start with a die shot of a single AMD Ryzen core.The main thing to notice here is of course the fact that each core has only one integer and FPU section, rather than splitting an FPU between two integer units. This represents a major design departure from earlier designs by AMD such as Bulldozer, Piledriver, etc, but is not entirely a surprise as Ryzen has been known (or at the very least, strongly suspected) to utilize such a config for quite some time now. This represents part of AMD's overall attempt to improve IPC by moving from a CMT (clustered multi-threading) model to a SMT (simultaneous multi-threading) based model, essentially trading two integer sections per core for one larger, better performing one. This will certainly go a long way towards raising single threaded performance and IPC.

All of that was already pretty much known, however. Of much more interest is the little section in the upper right labeled "Branch Prediction". AMD labels this as a "Neural Net Prediction" system, but in actual CPU-terms, it is a really fancy version of something known as a branch predictor. A branch predictor's job is to decide what a branch in the code will do before it actually happens, so the rest of the CPU can get ready for that reality. If it's wrong (and sometimes it is), the rest of the CPU has to spend time cleaning up after its missed prediction. A good branch predictor is not often wrong, though, and saves far more time than it looses by guessing correctly more often than not the outcome of the code path. AMD is essentially claiming that its branch predictor is much improved over previous iterations, and that its learning and training process for selection of outcomes is much more intelligent. Hence the name "Neural Net Prediction."

Moving on, let's take a look at a CCX (Core Complex, essentially a quad core module):AMD's main statement about the CCX module is that it is flexible, and allows for several adjustments to be made in the future with regards to L3 cache and core configuration. I would assume this is strong evidence that AMD has plans for Ryzen well beyond the initial "Summit Ridge" line of processors, if one were to be in the guessing game. Furthermore, AMD emphasizes the simplicity of their design. While it is true that Intel's 14nm process is a little more dense than AMD's (smaller), AMD says it has more than made up for this loss with a simpler, more efficient design that saves die space over Intel's present architecture. As such, AMD is confident it is finally on a "node parity" with Intel, something that we have not seen in quite a while, and should have a good many enthusiasts drooling at the very thought.

The final bit of AMD's presentation centered around a tech AMD has labeled "Precision Boost," which could be one of the most interesting slides of all.Precision boost appears to be a form of fine grained clock control for the processor, and will likely be used to enable energy savings and perhaps (in the case of XFR) enable a sort of automatic overclocking. Precision boost works hand in hand with AMD's monitoring tech, Pure Power, and clocks a CPU based on its "health and workload." It does this in fine grained 25 MHz increments that AMD says happen without "halts or queue drains." Real world performance of course has yet to be seen, but anything that saves energy or enables extra performance for the average user without delving too deep into overclocking is of course a welcome sight.

All in all, although a lot of this was suspected in the past, to see die shots support the claims and to have actual supportive statements from AMD itself, is always an encouraging thing.Source: PC Watch

40 Comments on AMD Ryzen Die Shot and New Architecture Details Revealed at ISSCC

PS: I'm kidding... or you'd best hope I am. Although if Vega sucks, I'm totally using that headline.

Anyhow, it wouldn't hurt to have your own emblem of some sort (with fog) at bottom of your articles.

good article

TPU article sources HotHardware article which btwHotHardware exact picture segmentation, different wording of course. They are more in-depth.

HotHardware article is based on PC Watch

The compactness of the article is nice.

The original source: pc.watch.impress.co.jp/docs/column/kaigai/1043349.html

Videocardz same day: videocardz.com/65774/more-details-about-amd-zen-cpu-core-revealed-at-isscc

PCGamesHardware.de: www.pcgameshardware.de/AMD-Zen-Codename-261795/News/Ryzen-vs-Skylake-Kaby-Lake-Chipflaeche-1220226/

www.dvhardware.net/article65964.html

It was all over the internet more then a week ago.

My article is indeed a simplification of material, and in some ways less in depth. I still think the key points were hit. The segmentation is identical but that's because I'm not the one breaking the news, simply reporting what others have found, really.

As for it being posted earlier, that does look to be the case, but I was unaware of it. Then again, I wasn't writing articles then either. :)

Thanks for the feedback. :)