Friday, April 5th 2019

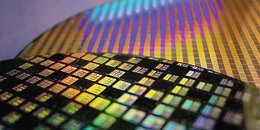

TSMC Completes 5 nm Design Infrastructure, Paving the Way for Silicon Advancement

TSMC announced they've completed the infrastructure design for the 5 nm process, which is the next step in silicon evolution when it comes to density and performance. TSMC's 5 nm process will leverage the company's second implementation of EUV (Extreme Ultra Violet) technology (after it's integrated in their 7 nm process first), allowing for improved yields and performance benefits.

According to TSMC, the 5 nm process will enable up to 1.8x the logic density of their 7 nm process, a 15% clock speed gain due to process improvements alone on an example Arm Cortex-A72 core, as well as SRAM and analog circuit area reduction, which means higher number of chips per wafer. The process is being geared for mobile, internet, and high performance computing applications. TSMC also provides online tools for silicon design flow scenarios that are optimized for their 5 nm process. Risk production is already ongoing.

Source:

TSMC

According to TSMC, the 5 nm process will enable up to 1.8x the logic density of their 7 nm process, a 15% clock speed gain due to process improvements alone on an example Arm Cortex-A72 core, as well as SRAM and analog circuit area reduction, which means higher number of chips per wafer. The process is being geared for mobile, internet, and high performance computing applications. TSMC also provides online tools for silicon design flow scenarios that are optimized for their 5 nm process. Risk production is already ongoing.

52 Comments on TSMC Completes 5 nm Design Infrastructure, Paving the Way for Silicon Advancement

In other words: a cloud user can easily allocate resources himself - without having neither admin knowledge nor admin rights on a server. And BTW: the "user" here doesn't have to be a human.

And who is "we"? What you understand (or don't understand) doesn't really change the reality. :-)