Monday, March 9th 2020

Rumor: Intel to Introduce Big.Little Architecture for Desktop With Alder Lake-S, New LGA 1700 Socket

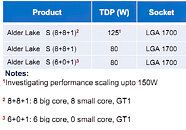

Hold on to your helmets: a wild rumor that Intel may be looking to introduce the same design considerations as they already did with their Lakefield architecture has appeared. According to momomo via Twitter (a user who has already shared many rumors and details in the PC hardware space) as well as some other sources, Intel is looking to bring a Big.Little-like design (which Intel calls Hybrid architecture) to the desktop platform in the form of Alder Lake-S, to be reportedly built on the 10 nm process. While Intel's Lakefield (especially geared for the mobile market) only sported four Atom (Intel's low power) Tremont cores combined with one high-performance Sunny Cove core, Alder Lake-S could sport as many as an 8+8 configuration, with a TDP currently set up to 80 W (and up to 125 W TDP is also set in the revealing slides with a disclosure regarding investigating performance scaling in up to 150 W TDP).

Should this actual Alder Lake-S product materialize in the 10 nm process, this could be a way for Intel to salvage what it can from the 10 nm process for the desktop platform. As we know from multiple reports on the state of Intel's 10 nm, yields and operating frequencies aren't close to what was expected, and Intel's CFO George Davis even said at last week's Morgan Stanley's Analyst Conference that their 10 nm process wouldn't be as profitable as even 22 nm, which does show that Intel is already looking past this process for their 7 nm deployment. A Big.Little design for a desktop architecture does seem like a more plausible design decision for a struggling process than a full 16-core monolithic die such as those Intel currently employs.The leaked slide also points to a new socket, LGA 1700, which would supersede the LGA 1200 that's being deployed with Comet Lake-S (10th gen) and which could feature support for Intel's Rocket Lake-S family (11th Gen). The leak also plays out a possible PCIe 4.0 support from Alder Lake-S, which could mean this is the first Intel architecture to sport this updated protocol, should it not debut with Rocket Lake-S already. Slightly logic, rational leaps mean that Intel could be looking at leveraging their Golden Cove (high performance) and Gracemont (Atom) CPU cores for this hybrid design.

Sources:

via Tom's Hardware, momomo @ Twitter, Ghost Motley @ Twitter, via Videocardz, Anandtech

Should this actual Alder Lake-S product materialize in the 10 nm process, this could be a way for Intel to salvage what it can from the 10 nm process for the desktop platform. As we know from multiple reports on the state of Intel's 10 nm, yields and operating frequencies aren't close to what was expected, and Intel's CFO George Davis even said at last week's Morgan Stanley's Analyst Conference that their 10 nm process wouldn't be as profitable as even 22 nm, which does show that Intel is already looking past this process for their 7 nm deployment. A Big.Little design for a desktop architecture does seem like a more plausible design decision for a struggling process than a full 16-core monolithic die such as those Intel currently employs.The leaked slide also points to a new socket, LGA 1700, which would supersede the LGA 1200 that's being deployed with Comet Lake-S (10th gen) and which could feature support for Intel's Rocket Lake-S family (11th Gen). The leak also plays out a possible PCIe 4.0 support from Alder Lake-S, which could mean this is the first Intel architecture to sport this updated protocol, should it not debut with Rocket Lake-S already. Slightly logic, rational leaps mean that Intel could be looking at leveraging their Golden Cove (high performance) and Gracemont (Atom) CPU cores for this hybrid design.

68 Comments on Rumor: Intel to Introduce Big.Little Architecture for Desktop With Alder Lake-S, New LGA 1700 Socket

i Mean AM4 has 1331 so i wonder what those extra 369 pins will bring to the table...

More Power? Faster/Wider Bandwich to the CPU? PCI-E 4-5? Better RAM performance?

I'd look at difference between FM2+ (906) and LGA115x.

Both provide almost the same connectivity - 16 PCIe lanes, 4 lane DMI/UMI, ~3 display outputs and dual channel RAM.

Both platforms had quite similar power ratings, yet PGA manages to do the same with less pins.

Judging by that my (un)educated guess is that PGA pins have better current capabilities.

906*1.27 ~= 1150

1331*1.27 ~= 1690

That also may mean that intel might finally create a proper SoC this time.

Read it - what's the point of the exercise against a 24-core or 32-core Ryzen ?

However, it might be good for mobile devices.

We don't know enough and most likely won't for at least another year.

As a comparison, the max core count or Ryzen 3000 wasn't officially revealed until about 9 months before launch or so, IIRC.

How are you going to fit a 150-watt or even an 80-watt SoC in that small nuke, is beyond me.

I forecast even further drop in Intel's market share in the coming years.

They completely lost connection with the reality and their focus is in unreal things.

Intel has always had a few reserved pins, as they tend to use at least some of them for more power once they bring out the second generation of a "platform".

Way better than the first run one big four little thing I wouldn't have bought, anyway.

Interesting times ahead no doubt.

@TheLostSwede not that many platforms got drop in upgrades from Intel, and I didn't mean you said pciex5 just others had rumoured it.

my idea was 8 big cores without HT, and having 8 small cores instead.

But it's the opposite for most of us. :)The leaked slide mentions high-end CPUs, but that generation will also include models will less cores and much lower power consumption.

The idea of high+low performance cores will be perfect for what I've mentioned.

For HEDT and so on - probably not so much. But I'm sure we'll find a way to use them.

And of course this is a perfect example of an architecture that can utilize OneAPI. So it's all beautifully coherent in the blue camp. We'll see how well this is executed.

The thing is, the 8 core processor with SMT will be less expensive to manufacturer and actually use less power than an 8+8 processor with no SMT. Big.Little makes no sense whatsoever on a desktop.

And if someone is so hung on not having SMT they can just disable it, no need for an entirely different processor.

Using only HT will obviously cost less, but that doesn't mean anything if we don't know the pro's of going with this solution.