Monday, May 4th 2020

Intel's Alder Lake Processors Could use Foveros 3D Stacking and Feature 16 Cores

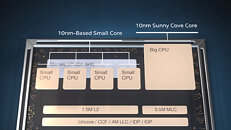

Intel is preparing lots of interesting designs for the future and it is slowly shaping their vision for the next generation of computing devices. Following the big.LITTLE design principle of Arm, Intel decided to try and build its version using x86-64 cores instead of Arm ones, called Lakefield. And we already have some information about the new Alder Lake CPUs based on Lakefield design that are set to be released in the future. Thanks to a report from Chrome Unboxed, who found the patches submitted to Chromium open-source browser, used as a base for many browsers like Google Chrome and new Microsoft Edge, there is a piece of potential information that suggests Alder Lake CPUs could arrive very soon.

Rumored to feature up to 16 cores, Alder Lake CPUs could present an x86 iteration of the big.LITTLE design, where one pairs eight "big" and eight "small" cores that are activated according to increased or decreased performance requirements, thus bringing the best of both worlds - power efficiency and performance. This design would be present on Intel's 3D packaging technology called Foveros. The Alder Lake CPU support patch was added on April 27th to the Chrome OS repository, which would indicate that Intel will be pushing these CPUs out relatively quickly. The commit message titled "add support for ADL gpiochip" contained the following: "On Alderlake platform, the pinctrl (gpiochip) driver label is "INTC105x:00", hence declare it properly." The Chrome Unboxed speculates that Alder Lake could come out in mid or late 2021, depending on how fast Intel could supply OEMs with enough volume.

Sources:

@chiakokhua (Twitter), Chrome Unboxed

Rumored to feature up to 16 cores, Alder Lake CPUs could present an x86 iteration of the big.LITTLE design, where one pairs eight "big" and eight "small" cores that are activated according to increased or decreased performance requirements, thus bringing the best of both worlds - power efficiency and performance. This design would be present on Intel's 3D packaging technology called Foveros. The Alder Lake CPU support patch was added on April 27th to the Chrome OS repository, which would indicate that Intel will be pushing these CPUs out relatively quickly. The commit message titled "add support for ADL gpiochip" contained the following: "On Alderlake platform, the pinctrl (gpiochip) driver label is "INTC105x:00", hence declare it properly." The Chrome Unboxed speculates that Alder Lake could come out in mid or late 2021, depending on how fast Intel could supply OEMs with enough volume.

40 Comments on Intel's Alder Lake Processors Could use Foveros 3D Stacking and Feature 16 Cores

How many upcoming CPU’s do they have?

Rocket Lake - Q4 2020

Alder Lake - 2021

Meteor Lake - 2022

:respect:

The common between them is that none of them has been released so far.

As an actual product though... seems like far fetched for consumer, and rather desperate too; is Intel saying it is economically feasible to deliver that much extra die space just so its not molten lava? And how about binning? That just got twice as complicated, no? Lots of unanswered questions...

Seams like they have a plan n all I'm not sure I like it though.

With big cores done right you can gate most of the cores off on light loads leaving a couple on but with burst processing and race to idle I dunno what is the point ,their competition doesn't need To go anywhere near this as the 4800/4900u show now ,their 5nm parts will be stiff competition.

Neither is the fact that that version of nothing doesn't happen often ie reading a page.

Watching videos or anything else is also never getting to 2 watts in the next few years.

I just hope this is just a garbage rumor and not for the Desktop DIY or HEDT systems. Esp if we talk on the HEDT processors, we know how Intel makes their XCC, HCC and LCC and similarly how AMD bins and makes 4, 8 Chiplet designs and all for maximum profits and scaling across their whole lineup of Silicon prowess and how Desktop systems SKUs are dependent on the same Wafer Lithography tech which are for their Datacenter, primary business.

1. AMD's Zen is superior;

2. 14nm with pluses;

3. ARM is superior to x86.

I guess BIG.little approach is trying to understand why Apple moves to ARM. And so on.

Intel will have very difficult decade to come.

Any other company in its place would struggle to survive.

Needs timestamp :( Skip to 1:48

videocardz.com/newz/intel-alder-lake-s-rumored-to-feature-lga1700-socket

> Alder Lake CPUs could arrive very soon

> Intel will be pushing these CPUs out relatively quickly

Also OP:

> Alder Lake could come out in mid or late 2021

The last thing does not follow the first two.

More cores equals more power used. And from that conclusion... its easy to draw other conclusions. Such as:

1. Windows scheduler and good allocation of workloads will be the key to gaining an advantage over other products

2. Intel's goal must be: faster when its needed (it can turbo high), fall back on little when possible (big cores can cool down and clear TDP budget for a new boost). Any other approach is not feasible, because then they are not competitive against stripped AND full fat performance cores.

4. A new reduction of base clocks on the BIG cores is likely, to clear more TDP headroom for turbo. Or maybe even dial back entirely to idle clock, some 800 mhz, and just have a turbo on top of that. Or maybe fully shut down, but I'm then thinking of latency problems.

So, using the cores at the same time will bring what advantage exactly? I'm not seeing it, do you? For this product to be viable, it needs to be better than either variant of the cores used in it. 8 fast and 8 slow cores are still worse than 16 regular ones at base clock, I reckon...

Interesting stuff indeed :) What I personally think is that Alder Lake is a way to get 10nm dies out that were planned anyway, and still keep competitive product across the whole stack. Forget 'glued together', Intel is going full scrapyard dive. It also confirms yet again that 10nm scales like shit into performance territory.

But since you didn't I'll tell you.

Intel couldn't fabricate s**t with the 10nm issues. So imagine them having 1,2...n projects aligned, ready for tapeout or in final shape, but with absolutely no posibility of turning them into a product.

Now, that things get a move on, they will pump out all the projects that should've released in the span of the last 4-5 years in two years, till 2022. So that is why you see every day a new product.

For mobile, that is laptops, 2 in 1, tablets and small PCs like NUCs this is going to be a nice product. The power advantage of using a low power core is there, no matter what anyone says.

For highend desktop, these are not ok and hopefully they have something else for that market, otherwise they will continue to lose marketshare.

A more sophisticated way would be to allow each core to power off certain elements within the core when not required. For example, powering off a FPU unit when not required, or half the L2 and L3 cache when not needed. But that doesn't allow marketing to scream 'MOAR CORES!' so that option is off the table.

Unfortunately for Intel it's just as much an issue of power use under load, I'm not thinking this will fix that.