Friday, June 26th 2020

Intel Lakefield Core i5-L16G7 Performance Benchmarks Leak

Performance benchmarks have started leaking for Intel-s upcoming Lakefield CPUs - low-power SoCs designed with Intel's latest technology. The Lakefield family of CPUs will make use of an Arm-similar big.LITTLE design, where this particular CPU, the Core i5-L16G7, will ship with four low-power "Tremond" cores and one large, high-performance "Sunny Cove" core for peak workloads. Built using Intel's Foveros stacking technology, these are the first chips to be built on Intel's modular platform, which should allow for pairing of I/O dies, chiplet-like CPU arrangements and memory in a 3D package. Physical distance reductions impact latency and power consumption, which should allow for an interesting design result.

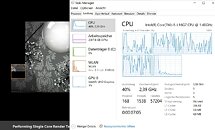

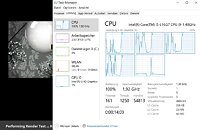

Notebookcheck has tested an Intel Lakefield Core i5-L16G7 CPU that's being deployed on upcoming Samsung's Galaxy Book S, and the results are sort of a mixed bag. For one, Intel's Lakefield seems to be around 67% slower than the company's previous ultra-low-power architecture, Amber Lake. Something of this might have been caused by the fact that the Lakefield CPU didn't boost towards its advertised 3.0 GHz; it only managed to reach 2.4 GHz, which obviously hampered performance. Perhaps pre-release silicon is the culprit, or perhaps it's the galaxy Book S that's been configured with more restrictive thermal and power characteristics than the chip was actually designed to run at. The chip did manage to run the FireStrike test beating the Amber Lake-based Acer Swift 7 by 23%, though, so not all is looking bleak.Looking at the screenshots, it does seem that most load is being distributed to the low power Tremond cores, which is obviously the idea in such a low-power design such as this (this assumes that the high-performance Sunny Cove core is last on the Task manager). It remains to be seen if hardware scheduling is being optimal, or if there is some sort of workload shuffle between cores due to OS mismanagement of the SoC - it is a possibility, perhaps, that the OS is shuffling data between cores, thus affecting performance benefits of L1 and L2 caches too aggressively, in an attempt to keep hotspot operating temperatures in check.There is a moment in the first benchmark though where the fifth core sees a surge in workload, moving up to 100% utilization, and then declines, giving way to more work on two other cores. This looks well in line with the expected use cases for the Sunny Cove core and Intel's thoughts on designing these chips: most users only require high performance in short bursts that need to provide as much system responsiveness as possible, such as web page loading and other similar workloads.

Source:

Notebookcheck

Notebookcheck has tested an Intel Lakefield Core i5-L16G7 CPU that's being deployed on upcoming Samsung's Galaxy Book S, and the results are sort of a mixed bag. For one, Intel's Lakefield seems to be around 67% slower than the company's previous ultra-low-power architecture, Amber Lake. Something of this might have been caused by the fact that the Lakefield CPU didn't boost towards its advertised 3.0 GHz; it only managed to reach 2.4 GHz, which obviously hampered performance. Perhaps pre-release silicon is the culprit, or perhaps it's the galaxy Book S that's been configured with more restrictive thermal and power characteristics than the chip was actually designed to run at. The chip did manage to run the FireStrike test beating the Amber Lake-based Acer Swift 7 by 23%, though, so not all is looking bleak.Looking at the screenshots, it does seem that most load is being distributed to the low power Tremond cores, which is obviously the idea in such a low-power design such as this (this assumes that the high-performance Sunny Cove core is last on the Task manager). It remains to be seen if hardware scheduling is being optimal, or if there is some sort of workload shuffle between cores due to OS mismanagement of the SoC - it is a possibility, perhaps, that the OS is shuffling data between cores, thus affecting performance benefits of L1 and L2 caches too aggressively, in an attempt to keep hotspot operating temperatures in check.There is a moment in the first benchmark though where the fifth core sees a surge in workload, moving up to 100% utilization, and then declines, giving way to more work on two other cores. This looks well in line with the expected use cases for the Sunny Cove core and Intel's thoughts on designing these chips: most users only require high performance in short bursts that need to provide as much system responsiveness as possible, such as web page loading and other similar workloads.

20 Comments on Intel Lakefield Core i5-L16G7 Performance Benchmarks Leak

There is no peak or burst performance to be had beyond whatever Intel already offered. Low power core does not enable higher power other core. So effectively the ceiling has just been lowered a bit.

Intel Core i5-1035G1 in 15 watts = 1533 points CB R20.

Intel Core i5-L16G7 in 7 watts = 479 points CB R20.

www.google.com/search?q=ryzen+7+4700u+cinebench+r20&oq=ryzen+7+4700u+cinebench+r20&aqs=chrome..69i57.11083j0j4&sourceid=chrome&ie=UTF-8

Open windows's setting page takes 10 second.

The Book S itself is well built, good keyboard , feather light , good screen .

But the CPU is a total drawback.

At least it can run Firestrike. :rolleyes:

Mmmkay, Intel.

B: it's working as intended and the big core isn't for any kind of sustained but only for ultra short and bursty workloads

Why don't the users object and sue Intel for making Celeron and Pentium, and this Core i5 ? :confused:

You know some people sue the coffee company for making too hot coffee that burns their hands........

Don't worry, once AMD reaches the end of road for the Zen development, AMD will be the same as Intel is today.

ARM and RISC is the future.

On the other hand, Cinebench is hardly this chip's intended use-case.

So I'm still going to hold off judging this one until reviewers have final silicon in hand.

This is a pretty sad display of ingenui... err desperationYes, so then you take a low power chip, they've had that since forever and they mostly perform better. Higher performance is more time in idle, so its really more of the same.

See, the fact is, this design is also not cheaper than a single low power equivalent... so they've just added complexity for what exactly?

I mean... a full day of battery life... I might be stupid, but isn't the key then to improve the battery a little bit? This is just an awful race to the bottom just to maintain some silly form factor.