Qualcomm Said to be Moving to TSMC for 3 nm Chips

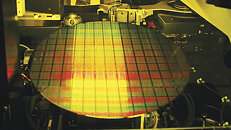

Although nothing has been officially confirmed by Qualcomm, it looks like the company will be moving away from Samsung for its 3 nm based chips, in favour of TSMC. The Elec also mentions that Qualcomm has moved some of its Snapdragon 8 Gen 1 production to TSMC, something that has already been hitting the rumour mill. The first batch of 4 nm Snapdragon 8 Gen 1 chips are said to already have entered the early stages of production. The main reason for the move is said to be poor yields by Samsung Foundry on its 4 nm node.

The yield rates are said to be a measly 35 percent for the Snapdragon 8 Gen 1, with Samsung's Exynos 2200 having even lower yields. This also helps explain why Samsung's mobile division has decided to limit the availability of its Exynos 2200 based phones to only a few regions. Apparently Qualcomm had to send staff over to Korea to help get the yields up to their current rate, but it's not hard to see why the company is shifting back to TSMC, as a 35 percent yield rate is simply not acceptable. Samsung is said to be auditing Samsung Foundry to find out what has gone wrong, as anything below 80-90 percent in terms of yield rate is simply not acceptable for mass production. Qualcomm will apparently continue to use Samsung Foundry for its 7 nm RF chips, where the yields must be within industry norms.

The yield rates are said to be a measly 35 percent for the Snapdragon 8 Gen 1, with Samsung's Exynos 2200 having even lower yields. This also helps explain why Samsung's mobile division has decided to limit the availability of its Exynos 2200 based phones to only a few regions. Apparently Qualcomm had to send staff over to Korea to help get the yields up to their current rate, but it's not hard to see why the company is shifting back to TSMC, as a 35 percent yield rate is simply not acceptable. Samsung is said to be auditing Samsung Foundry to find out what has gone wrong, as anything below 80-90 percent in terms of yield rate is simply not acceptable for mass production. Qualcomm will apparently continue to use Samsung Foundry for its 7 nm RF chips, where the yields must be within industry norms.