Monday, April 13th 2015

AMD "Zen" A Monolithic Core Design

AMD's upcoming "Zen" architecture will see a major change in the way the company designs its CPU cores. It will be a departure from the "module" core design introduced with "Bulldozer," in which two cores with shared resources constitute the indivisible unit of a multi-core processor. A "Zen" core will have dedicated resources in a way things used to be before "Bulldozer," and only the last-level cache (L3 cache), will be shared between cores. "Zen" will also implement SMT, much in the same way as Intel processors do, with HyperThreading Technology.

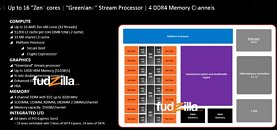

The first implementation of "Zen" will be an insanely powerful APU (on paper anyway), featuring 16 physical "Zen" CPU cores, 32 logical CPUs enabled with SMT, 512 KB dedicated L2 cache per core, and 32 MB of shared L3 cache. The CPU's ISA instruction set will see a spring-cleaning, with the removal of underused instruction-sets, and the introduction of new ones. Other features on this APU are equally surprising - a quad-channel DDR4 integrated memory controller, a separate HBM (high-bandwidth memory) controller dedicated to the integrated graphics, with up to 512 GB/s bandwidth, and an integrated graphics core featuring "Greenland-class" stream processors. Given that AMD is able to build 7-billion transistor GPUs on existing 28 nm processes, building an APU with these chops doesn't sound far-fetched. The company could still have to rely on a newer fab.

Source:

FudZilla

The first implementation of "Zen" will be an insanely powerful APU (on paper anyway), featuring 16 physical "Zen" CPU cores, 32 logical CPUs enabled with SMT, 512 KB dedicated L2 cache per core, and 32 MB of shared L3 cache. The CPU's ISA instruction set will see a spring-cleaning, with the removal of underused instruction-sets, and the introduction of new ones. Other features on this APU are equally surprising - a quad-channel DDR4 integrated memory controller, a separate HBM (high-bandwidth memory) controller dedicated to the integrated graphics, with up to 512 GB/s bandwidth, and an integrated graphics core featuring "Greenland-class" stream processors. Given that AMD is able to build 7-billion transistor GPUs on existing 28 nm processes, building an APU with these chops doesn't sound far-fetched. The company could still have to rely on a newer fab.

102 Comments on AMD "Zen" A Monolithic Core Design

I find this very interesting in general that it's an SoC and has a lot of functionality. Board layouts with a performance-level SoC should be *very* interesting to see. (Take a peak at Asus' C2750 workstation/nas board.) Since there would be no north bridge or pch-like chips, it allows for more area to do other things directly off PCI-E and not use the PCH/(chipset/SB) for PCI-E lanes which introduces latency.

All in all, I think this is great. I would love to see where this goes.

I guess that is where we are headed though, now that progress in single core speed has stalled. It sucks for computations that can't be done in parallel.

I'm not sure why everyone is getting their panties in a twist over server chips.

It is two chips bound on a common substrate, under a common heatsink, in an MCM package.With the pin count and the fact that it has HBM on-package, I would sincerely doubt that this would be a conventional socketed processor. More likely the CPU + HBM would be an interposer module, just as the GPU+HBM are expected to be.That would be my estimation also. The GPU would undoubtedly be for GPGPU ( co-processor) duty - a fairly conventional answer to Xeon Phi or Nvidia's planned Volta + ARM product lines.

It could be :laugh:

Hmm... 50-100% more shaders than the PS4's GPU, using GCN 1.3+ tech with half-rate DP, 16GB HBM with a 512GB/s interface, 16 CPU cores/32 threads, 4 of these on a liquid-cooled blade with 64/128GB of DDR4-3200 per chip, 16 blades per 4U cabinet, 6-8 cabinets per rack ... Holy HPC servers, Batman!

I doubt this will be built on anything older than GF or Samsung 20/16nm process.

Consider AM1 with 722 contacts. That's only for 8? PCI-E lanes, Gigabit, 2 sata ports, graphics output, and only 1 memory channel. Now compare that is a beefy SoC. 60 PCI-E lanes, 2 GBe maybe, ~6 SATA, 4 DDR4 memory channels, and maybe a little more for display output. Seriously, I think 2000 contacts is going to be optimistic. I wouldn't be surprised if it was closer to 3k if this is legit.

With that said, I'll sit back, wait, and see. Anything to add some competition in the market.

Edit: It does seem that PCI-E and SATA share the same circuitry, so more SATA means less PCI-E and more PCI-E means less SATA. I could live with that.

Btw, if I understand this correctly, AMD will have their own version of hyperthreading this time around? I love this thing with Intel CPU's. It's the reson why my ancient Core i7 920 is still so competitive. It churns out 8 threads and that still works incredibly well with file compression, video coding, audio conversion, large image processing etc. I know it's not like a full core on it's own but it certainly makes a huge difference.

K7 was over 15 years ago and things change, the economy was different, banks were lending more, interest rates were higher, tech companies were showered with sponsorship money and loan money, there was the big technology bubble, there was no big internet tech websites, you had to buy specialist magazines to learn about upcoming products and technologies. Desktop machines were selling like hotcakes and nobody anticipated mobile marketing taking off. Keller can't snap his fingers and rewind time because the world was different back then.

Aka its just some marketing hype and there will be no product that is made.

As for marketing hype, I doubt this came from AMD - more likely clickbait from the usual suspects - and bearing in mind Faud's (Fudzilla) strike rate, I'd be more than a little wary of its veracity.

The choices that we have, help us out in the long run. I also like to use AMD GPUs.

AMD is necessary in this market.