Wednesday, August 19th 2015

Intel Skylake Microarchitecture Detailed

The "Skylake" CPU microarchitecture is as much important to Intel as "Sandy Bridge" was, a few years ago. It allows Intel to facilitate mainstream adoption of the DDR4 memory standard (with DDR3 backwards compatibility encouraging cheap upgrades), and gives users IPC increases over older architectures. While users of Core "Haswell" processors and reasonably fast DDR3 memory will find "Skylake" a hard-sell, it should look appealing to users of much older chips, such as "Lynnfield," and perhaps even "Sandy Bridge."

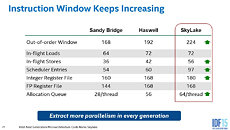

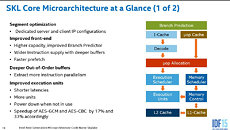

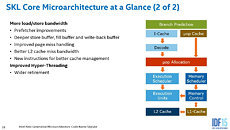

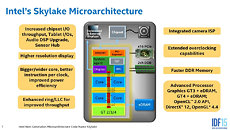

The "Skylake" core is bigger than "Haswell," owing to wider pipelines, prefetcher improvements, more execution units, a bigger front-end with a higher-capacity branch predictor, cache optimizations, and an update to the way HyperThreading works. The instruction window is nearly 1.5x the size of Sandy Bridge, with an out-of-order execution window size of 224 (vs. 168 on Sandy Bridge), load/store sizes of 72/56 (vs. 64/36 on Sandy Bridge), 97 scheduler entries (vs. 56 on Sandy Bridge), and an allocation queue size of 64/thread (vs. 28/thread). The platform of "Skylake" is similar to that of its predecessor, with four notable changes - an integrated camera ISP with the chipset, DDR4 memory support, double the chipset bus bandwidth (64 Gb/s), and eDRAM support on certain CPU SKUs.

Source:

HotHardware

The "Skylake" core is bigger than "Haswell," owing to wider pipelines, prefetcher improvements, more execution units, a bigger front-end with a higher-capacity branch predictor, cache optimizations, and an update to the way HyperThreading works. The instruction window is nearly 1.5x the size of Sandy Bridge, with an out-of-order execution window size of 224 (vs. 168 on Sandy Bridge), load/store sizes of 72/56 (vs. 64/36 on Sandy Bridge), 97 scheduler entries (vs. 56 on Sandy Bridge), and an allocation queue size of 64/thread (vs. 28/thread). The platform of "Skylake" is similar to that of its predecessor, with four notable changes - an integrated camera ISP with the chipset, DDR4 memory support, double the chipset bus bandwidth (64 Gb/s), and eDRAM support on certain CPU SKUs.

6 Comments on Intel Skylake Microarchitecture Detailed

Fu**ing bastards lock the overclocking in the first place!

i might be a disgraphic..