Sunday, August 9th 2020

AMD Files Patent for its Own big.LITTLE Tech - Processor Clusters

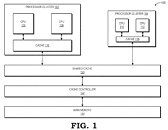

In a sign of AMD's answer to Intel Hybrid tech being quite far away from implementation in a product, the company filed patents to a rival/similar technology only as recently as June 30, 2020, with the patent application being dug up by Underfox. The patent calls for a multi-core processor topology with two kinds of CPU cores - a "high-feature" core (big core), and a "low-feature" one (small core).

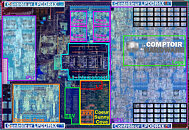

Here's where AMD's design is different: it calls for closely integrated groups of the two kinds of cores (one big core, and one small core), called "Processor Clusters." The dedicated L1 caches of the big and small cores in each group shadow data, while an L2 cache is shared between the two cores. Several such big+small Processor Clusters sit across a die, sharing the chip's last-level cache (L3 cache). This is unlike Intel's Hybrid design, where the big and small cores are spread apart on the die, with little cache coherency (Lakefield die-shot by le Comptoir du Hardware below). The patent also details the workflow of how the processor reconciles the ISA differences between the two core types.

Source:

Tom's Hardware

Here's where AMD's design is different: it calls for closely integrated groups of the two kinds of cores (one big core, and one small core), called "Processor Clusters." The dedicated L1 caches of the big and small cores in each group shadow data, while an L2 cache is shared between the two cores. Several such big+small Processor Clusters sit across a die, sharing the chip's last-level cache (L3 cache). This is unlike Intel's Hybrid design, where the big and small cores are spread apart on the die, with little cache coherency (Lakefield die-shot by le Comptoir du Hardware below). The patent also details the workflow of how the processor reconciles the ISA differences between the two core types.

20 Comments on AMD Files Patent for its Own big.LITTLE Tech - Processor Clusters

However, Intel plans to use the same design on desktops. Would there be some advantages if ALL cores worked at the same time, or say both in pair (since it's here described as such), or it's exclusively either/or situation?

Through my general idea, having 2 cores produced to work in two 'flavours' (because we do have frequency lowering and boosts and whatnot for energy efficient already) seems unreasonable. They 'look' like more expensive to design and occupy more place for nothing.

Some core features/space 'look' as needed to be present on all cores, which seems wasteful. Or perhaps yield for small ones is such good and production cheap that it comes to some calculation?

Now, this whole post is because the fact that both Intel/AMD are talking (or even starting production) about this approach - well, I know very little about pricing or advantages of this 'innovation' - only about ARM cores, where it's kinda obvious - or is it, after all?

I would like to know why, that's all - can anyone who understands this write some short Pros/Cons or something. It will be appreciated...

But having a big and a little core share L2 cache is a bad idea. This will make the cache less efficient and possibly increase the cache latency. It will also make it harder for the scheduler to predict the performance. I certainly hope a such design (if it is realized at all) is limited to low power laptops and APUs.Just open task manager and look at all the threads in there, there may be thousands of threads tied to background processes, drivers, services etc.

I still think its an interesting route, and I also think AMD has a better (again) plan when it comes to yields and product stacks. The mess of Intel Alder Lake core configurations... holy crap. This however, looks sensible. It is likely you also want the better small cores with the better big cores and they're still sticking to chiplets this way.

In some way this also reminds of Bulldozer/Piledriver, except now the bottleneck is just the large core perf. So yes, we could think 'why bother' and I get that, part of me does it too. But when you take Intel's bursty CPU management the idea suddenly isn't so strange. And AMD is fast approaching that as well, even if their boost is more intelligent and bases are higher, they still do get warm on a tiny surface area.

There are already Arm CPUs with 3 different types of cores (small, medium, large as opposed to just big, little) and the heterogeneous core count of Alder Lake makes me strongly suspect it's also designed for this sort of flexibility. Whereas AMD's design doesn't seem much more than, to borrow an old and incorrect analogy, "glue".

Yeah, it matters.

It's the same logic with "If we all took 1 minute showers we'd save so much water and money". Yeah, maybe we would but to the individual it makes no difference.