Friday, August 20th 2021

No PCIe Gen5 for "Raphael," Says Gigabyte's Leaked Socket AM5 Documentation

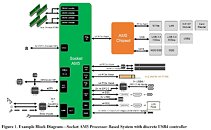

AMD might fall behind Intel on PCI-Express Gen 5 support, say sources familiar with the recent GIGABYTE ransomware attack and ensuing leak of confidential documents. If you recall, AMD had extensively marketed the fact that it was first-to-market with PCI-Express Gen 4, over a year ahead of Intel's "Rocket Lake" processor. The platform block-diagram for Socket AM5 states that the AM5 SoC puts out a total of 28 PCI-Express Gen 4 lanes. 16 of these are allocated toward PCI-Express discrete graphics, 4 toward a CPU-attached M.2 NVMe slot, another 4 lanes toward a discrete USB4 controller, and the remaining 4 lanes as chipset-bus.

Socket AM5 SoCs appear to have an additional 4 lanes to spare than the outgoing "Matisse" and "Vermeer" SoCs, which on higher-end platforms are used up by the USB4 controller, but can be left unused for the purpose, and instead wired to an additional M.2 NVMe slot on lower-end motherboards. Thankfully, memory is one area where AMD will maintain parity with Intel, as Socket AM5 is being designed for dual-channel DDR5. The other SoC-integrated I/O, as well as I/O from the chipset, appear to be identical to "Vermeer," with minor exceptions such as support for 20 Gbps USB 3.2x2. The Socket has preparation for display I/O for APUs from the generation. Intel's upcoming "Alder Lake-S" processor implements PCI-Express Gen 5, but only for the 16-lane PEG port. The CPU-attached NVMe slot, as well as downstream PCIe connectivity, are limited to PCIe Gen 4.

Socket AM5 SoCs appear to have an additional 4 lanes to spare than the outgoing "Matisse" and "Vermeer" SoCs, which on higher-end platforms are used up by the USB4 controller, but can be left unused for the purpose, and instead wired to an additional M.2 NVMe slot on lower-end motherboards. Thankfully, memory is one area where AMD will maintain parity with Intel, as Socket AM5 is being designed for dual-channel DDR5. The other SoC-integrated I/O, as well as I/O from the chipset, appear to be identical to "Vermeer," with minor exceptions such as support for 20 Gbps USB 3.2x2. The Socket has preparation for display I/O for APUs from the generation. Intel's upcoming "Alder Lake-S" processor implements PCI-Express Gen 5, but only for the 16-lane PEG port. The CPU-attached NVMe slot, as well as downstream PCIe connectivity, are limited to PCIe Gen 4.

118 Comments on No PCIe Gen5 for "Raphael," Says Gigabyte's Leaked Socket AM5 Documentation

If staying on Gen 4 lets them avoid things like x570s chipset fan, it's the right choice

With the distance of PCIe 5.0 lanes being almost half of PCIe 4.0 lanes before you need redrivers, it's not likely it'll be widely adopted on all interfaces, especially on consumer motherboards.

Oops in z590 PCIe is 3.0...Haha! That's mean most short transfer to PCIe 5.0 or direct jump from PCIe 3.0 to PCIe 5.0 in chipsets PCIe lines.

add atx12vo to the mix, we can expect them to be helluva expensive :roll:

Will we see massively overpriced ultra-premium PCIe 5.0 m.2 drives? Sure. Will they be tangibly better than 4.0, or supplant them in the market? Highly unlikely - they'll be a push for higher ASPs and more premium branding. As @TheLostSwede says, the overall industry is likely to slowly move to adopting 4.0 for AICs and controllers, but this is a process that takes time. The main reasons for it taking time is design and implementation costs, as well as potentially limiting customer bases if the goal is to limit lane counts. PCIe 5.0 does zero to alleviate any of this, and arguably exacerbates things instead - moving controllers and AICs to 5.0 will be more expensive than moving them to 4.0, and given how few things actually need the bandwidth, there's less incentive for OEMs to take on that cost. I agree that we'll likely see USB4 and 10GbE move to 4.0 in relatively short order (i.e. over the next couple of years), but even for high-bandwidth uses like that, 5.0 is going to take a lot of time to make any kind of sense. That leaves SSDs (as I said, likely, but rather pointless unless someone invents flash that doesn't need as much parallelism, which ... yeah, that isn't happening any time soon) and GPUs (which also don't need the bandwidth, and will arguably need less bandwidth with adoption of DirectStorage and any competing APIs).

PCIe 5.0 makes perfect sense for datacenters where more bandwidth can always be put to use, and more accelerators, controllers, NICs and AICs per CPU is always better. But for end users? I doubt we'll see even a single 5.0 product with any tangible benefits from that interface in the next 3-4 years.

Where is retimers?

P.S. Right now I don't even care about PCIe 4, but before the end of 2022 I must build or buy a new office PC, it's an obligatory 5 year cycle (actually it will already be delayed). After those 5 years the PCs find their way home, I know it sounds selfish, but the offsprings are more than happy with a GPU upgrade. That's why I'll follow the PCIe 5 and DDR5 path and cost won't be a big issue. Due to covid I'll get a subsidy (I hope it's the right term for business financial aid) and like always a tax write-off.

What Intel clearly did right here, was to put a much fatter pipe to the chipset, not only by going to PCIe 4.0 (as DMI is pretty much PCIe), but also by moving to eight lanes, so compared to the previous generation, this is quadrupling the available bandwidth between the chipset and the CPU. However, it looks like it's needed as well, since one interesting thing that's being revealed here is that Intel seems to be ready to push 5Gbps Ethernet, in addition to more and faster USB ports and obviously those 12 PCIe 4.0 lanes, which we'll see Thunderbolt or USB4 hang off of.

An eight lane PCIe 4.0 retimer from TI costs US$23.50 each, if you buy 1k units.

www.ti.com/product/DS160PT801#order-quality

A four channel PCIe 4.0 redriver is much more reasonable at under $4 each at 1k, but you might end up needing a few of those dotted around a board.

www.ti.com/product/SN75LVPE4410#order-quality

Also avoids the need for expensive 8 layer PCBs which will be pretty much mandatory for PCIe 5.0...

AMD might skip PCIe 5 for the consumers, altogether.

For one, PCB's don't have wires, they have multiple layers with copper traces, but you can't simply make those traces thicker or wider, it's not enough to improve the signal. For PCIe 5.0 we're talking transfer rates of ~4GB/sec, per direction, per lane, so any kind of interference is going to mess that up.

Yes, the board makers shifted to more advanced PCB materials with PCIe 4.0, but this isn't directly related to the copper traces, but rather to the material the PCB is made from, to try and reduce interference and noise.

Keep in mind that one retimer isn't going to be enough if you want all slots on a motherboard to be PCIe 5.0, you're most likely going to need a couple of them, so that's $50 or more on the retail price of a motherboard for something that's unlikely to benefit any consumer for at least the next five years.

The average ATX size X570 board seem to use three to five redrivers, depending on the design. That alone is $12 or more, which I'm expecting will still be required in combination with the retimers.

The redrivers have improved since the X570 chipset launched, as it seems early redrivers could only handle two PCIe lanes, whereas more recent ones seems to be able to handle up to four PCIe lanes, so that might allow for some cost savings.

Some interesting bits here as well, which shows the difference between a redriver and a retimer.

pcisig.com/pci-express%C2%AE-retimers-vs-redrivers-eye-popping-difference

Love engineering groups that don't use metric...

Anyhow, this shows that moving from PCIe 4.0 to 5.0 cuts about 40% of the trance length due to signal loss.

Right now, high-end motherboards are using low-loss PCBs.

Keep in mind that this is trace length, which is much longer than the distance of the slot from the chipset/CPU.

pcisig.com/retimers-rescue-webinar-pci-sig%C2%AE-qa

The shared prices above just prove that there is no future for the PCIe 5 standard because it will make the boards prohibitively expensive, which is not what we need.

We need PCIe 4 for now and the next several years.

Most people still have access to primitive 500 MB/s read/write SSDs, so even PCIe 4 is a giant step forwards.But the redrivers/retimers costs don't directly go in the final retail price for the consumer - they still get a very significant profit margin on top.

Also, PCIe bandwidth demands don't scale linearly with GPU power. Not even close. A 2-2.5x increase in render performance does not mean a 2-2.5x increase in bandwidth demands. Most likely bandwidth demands will increase by a relatively small percentage, as they have been doing with each generation for a decade. There's zero indication that this will suddenly become a major bottleneck. The 2080 Ti was the first GPU where there was a notable (>1%) difference between PCIe 3.0 x16 and x8. And that of course doesn't mean that it needed the full bandwidth of x16, just that x8 was slightly less than optimal - 9 or 10 lanes might have been completely sufficient. PCIe 4.0 x16 has doubled what was already sufficient, in other words there is still tons of headroom, and there is <1% difference in performance for the current fastest GPUs between 3.0 and 4.0 x16. There's no reason for 4.0 to remain a budget option, as it will in all likelihood provide 100% of the performance of any PCIe 5.0 GPU launched in the next five years (if not longer). All the while it will have cheaper motherboards.

PCIe 4.0 was indeed late, but not in a way that mattered to end users in any way whatsoever. It held datacenters back, but the rest of us? Nope. And 4.0 is still plenty for us, and will be for the next 5+ years in all but the most extreme cases.

Heck, it's the same with cables - just because USB-C cables are now ubiquitous doesn't mean that they're the same price as old USB 2.0 micro-B cables. They never will be, as there are more materials, more complex production techniques, and both are at commodity volumes already. (You might find USB 2.0-only, low amperage usb-C cables at close to the same costs as USB 2.0 micro-B cables, but it's not going to hit parity, ever.)