Friday, August 20th 2021

No PCIe Gen5 for "Raphael," Says Gigabyte's Leaked Socket AM5 Documentation

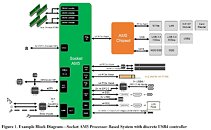

AMD might fall behind Intel on PCI-Express Gen 5 support, say sources familiar with the recent GIGABYTE ransomware attack and ensuing leak of confidential documents. If you recall, AMD had extensively marketed the fact that it was first-to-market with PCI-Express Gen 4, over a year ahead of Intel's "Rocket Lake" processor. The platform block-diagram for Socket AM5 states that the AM5 SoC puts out a total of 28 PCI-Express Gen 4 lanes. 16 of these are allocated toward PCI-Express discrete graphics, 4 toward a CPU-attached M.2 NVMe slot, another 4 lanes toward a discrete USB4 controller, and the remaining 4 lanes as chipset-bus.

Socket AM5 SoCs appear to have an additional 4 lanes to spare than the outgoing "Matisse" and "Vermeer" SoCs, which on higher-end platforms are used up by the USB4 controller, but can be left unused for the purpose, and instead wired to an additional M.2 NVMe slot on lower-end motherboards. Thankfully, memory is one area where AMD will maintain parity with Intel, as Socket AM5 is being designed for dual-channel DDR5. The other SoC-integrated I/O, as well as I/O from the chipset, appear to be identical to "Vermeer," with minor exceptions such as support for 20 Gbps USB 3.2x2. The Socket has preparation for display I/O for APUs from the generation. Intel's upcoming "Alder Lake-S" processor implements PCI-Express Gen 5, but only for the 16-lane PEG port. The CPU-attached NVMe slot, as well as downstream PCIe connectivity, are limited to PCIe Gen 4.

Socket AM5 SoCs appear to have an additional 4 lanes to spare than the outgoing "Matisse" and "Vermeer" SoCs, which on higher-end platforms are used up by the USB4 controller, but can be left unused for the purpose, and instead wired to an additional M.2 NVMe slot on lower-end motherboards. Thankfully, memory is one area where AMD will maintain parity with Intel, as Socket AM5 is being designed for dual-channel DDR5. The other SoC-integrated I/O, as well as I/O from the chipset, appear to be identical to "Vermeer," with minor exceptions such as support for 20 Gbps USB 3.2x2. The Socket has preparation for display I/O for APUs from the generation. Intel's upcoming "Alder Lake-S" processor implements PCI-Express Gen 5, but only for the 16-lane PEG port. The CPU-attached NVMe slot, as well as downstream PCIe connectivity, are limited to PCIe Gen 4.

118 Comments on No PCIe Gen5 for "Raphael," Says Gigabyte's Leaked Socket AM5 Documentation

However, I am surprised they didn't widened the interface to the chipset, but I guess the workaround was to add four more PCIe 4.0 lanes to the CPU for USB4/Thunderbolt support.

This also makes it clear that AMD is going for DP 2.0.

But I doubt PCIe 5.0 will bring anything interesting in the first year or two. We are fully covered on SSDs and probably going PCIe 5.0 will have minimal impact on graphics card performance. As always.

Also considering that PCIe 4.0 was used on SSDs, not to push higher speeds at lower prices, but instead push prices higher, who really needs an 1TB SSD that can score 14GB/sec sequencial speed, if it costs $300-$400?

We didn't saw cheaper PCIe 4.0 SSDs running on PCIe 4.0 x2 or even PCIe 4.0 x1. We saw just more expensive PCIe 4.0 x4 SSDs.

We show motherboards with AMD 570 to have 3 PCIe x16 slots and two of them connected to the chipset, instead of the two first be connected to the CPU and have the option to split PCIe lanes from X16 to x8 + x8. I was talking back then about "micro ATX boards, build to look like full ATX boards" and many where totally against this opinion.

Anyway, I doubt what you say and it should be basic logic to prevail over higher profit margins.

You're aware it takes some time to make these things, right? It's not just an interface you can easily swap out when you feel like it.

And as to your other comment, we are actually starting to see devices that are using fewer lanes. Look at Marvell's new AQC113 10Gbps Ethernet controller, it can use a single PCIe 4.0 lane for 10Gbps speeds, instead of four PCIe 3.0 lanes. On top of that, it's in a BGA packaging instead of FCBGA, which makes it cheaper to produce. So in other words, we are seeing cheaper devices that use fewer lanes, but it doesn't happen over night.

graphic card of the actual Gen use Gen4 i know ... but ... :cry:

so, AMD will not offer that and maybe focus on something else? fine by me...

I can include smiles too :p

My English are far from perfect, but I am pretty sure that "we didn't see manufacturers really using that standard" is somewhat different from "equals no support to you".

SSD manufacturers came up with PCIe 4.0 models that where not much better than PCIe 3.0 models, with the exception of sequential speeds. If I am not mistaken, Samsung didn't really rushed to come out with PCIe 4.0 solutions either. And as for PCIe 4.0 with graphics cards, it's just normal for the manufacturers to use the latest version of the bus, but my point was that 4.0 doesn't offer much compared to 3.0 version in 3D performance, something that is usually the case in all those last years. Not just this last generation.

Now my point exactly is that. Now that Intel will come out with PCIe 5.0 support, we will see how difficult it is to create PCIe 5.0 SSDs that are clearly faster than previous generations SSDs in about every benchmark. I wouldn't remember your post by then, I hope you would and you would mention me either to tell me that I was wrong, or either to tell me that probably I was right.

About that AQC113. Was it available after AM4 came out or after Intel supported PCIe 4.0? If it was way before Intel supported 4.0, then we have an example. But still I believe it is an exception, not the rule.

Finally, more smiles!!!!!

:peace::clap::pimp::toast::laugh::roll::love:

That's the problem with adopting new standards in open ecosystems with large install bases - if you break compatibility, you shrink your potential customer base dramatically.

Overall, I think this is a very good choice on AMD's part. The potential benefits of this are so far in the future that it wouldn't make sense, and the price increase for motherboards (and development costs for CPUs and chipsets) would inevitably be passed on to customers. No thanks. PCIe 4.0 is plenty fast. I'd like more options to bifurcate instead, but 5.0 can wait for quite a few years.

People only think about this in the context of current graphics APIs and how they interact with GPUs. Well, of course there is mostly nothing to be gained by increasing the speed of PCI-e because those APIs are stuck on top of the model of "PCI-e is slow".

In more plain language: given that software isn't making real use of PCIe 3.0, and we have 4.0 already widely available, what benefit does 5.0 bring, even in the future?

Motherboard manufacturers unite against Intel's efficient PSU plans | PC Gamer

Though, take it with a grain of salt, as always.I'd argue the overwhelming majority of people don't even have any kind of PCIE 4.0 SSD at all, either from that first wave which were basically 3.0-era with 4.0 controller or the newer ones.

(Yes, obviously the need for flash parallelism and the cost inherent to this is also an issue restricting performance, but most decent 3.0 drives can maintain random 4k speeds far above what most applications will ever come close to making use of.)Sure, but what does that have to do with motherboard prices? Last I checked, the PSU is separate ;)

And I would expect motherboard makers to push back - they're a notoriously conservative lot (plus are corporations producing largely commodity products with low margins under late-stage capitalism), and have no interest in taking on the expenditure of adapting to new standards just because they would benefit consumers, the environment, etc. My hope: that OEMs already using 12VO-like proprietary solutions shift over to 12VO, leading to opportunities for slow and steady growth in replacement PSUs, opening the door for niche motherboards as well. 12VO would be great for ITX boards, saving potentially a lot of board space with only the 10-pin connector needed (and the necessary buck converters being small and quite flexible in where they are placed). But I don't have any real hope for this becoming widely available in the next 5+ years, sadly.

As for the utility of PCI-E Gen 5, well, the more the better all the time. But on the GFX side, Devs try to make sure PCI-E is a non-issue. It was quite easy because most of the market were on Gen3 16X. Theses day with the lower cards like the 6600XT that are only 8X, that change a bit. But before things like Direct Storage and sampler feedback. (As long as the storage can follow).

With Sampler Feedback, you could load twice the amount of texture mipmap during a standard frame duration. (Or load the same amount of data faster to get higher fps since you don't have to wait for the data).

The more bandwidth the better. Build it and they will come. If on Intel, PCIE Gen 5 cost just a little bit more, it should be one of the selling point. Not the main one indeed, but still one of it.

Definitely behind Intel's Gen5 but arguably still waaaay more than any consumer is going to need for the shelf-life of these first-gen AM5 CPUs and chipsets.

The issue with SSDs are not the controllers, but the NAND flash. We should see some improvements as the NAND flash makers stack more layers, but even so, the technology is quite limited if you want faster random speeds and that's one of the reasons Intel was working on 3D XPoint memory with Micron, was later became Optane, no? It might not quite have worked out, but consumer SSDs are using a type of flash memory that was never really intended for what it's being used as today, yet it has scaled amazingly in what is just over a decade of SSDs taking over from spinning rust in just about every computer you can buy today.

Also, do you have any idea how long it takes to develop any kind of "chip" used in a modern computer or other device? It's not something you throw together in five minutes. In all fairness, the only reason there was a PCIe 4.0 NVMe controller so close to AMD's X570 launch, was because AMD went to Phison and asked them to make something and gave them some cash to do it. It was what I'd call "cobbled together" as it ran hot, it was technically a PCIe 3.0, but with a PCIe 4.0 bus strapped on to it. Hence why it performed as it did. It was also produced on a node that wasn't really meant for something to handle the amount of data that the PCIe 4.0 can deliver, so it ran hot as anything.

How long have we used PCIe 3.0 and how long did it take until GPUs took advantage of the bus? We pretty much had to get to an GTX 1080 for it to make a difference against PCIe 1.1 at 16 lanes, based on testing by TPU. So we're obviously going to see a similar slow transition, unless something major happens in GPU design where they can take more of an advantage of the bus. So obviously the generational difference is going to be even smaller with 4.0 and 5.0 as long as everything else stays the same.

www.techpowerup.com/review/nvidia-geforce-gtx-1080-pci-express-scaling/24.html

Did you even read the stuff that was announced these past few days? Intel will only have PCIe 5.0 for the PEG slot initially, so you won't see any SSD support for their first consumer platform, which makes this argument completely moot. So maybe end of 2022 or sometime in 2023 we'll see the first PCIe 5.0 consumer SSDs.

The AQC113 was launched a couple of months ago, but why does it matter if Intel supported PCIe 4.0 or not? We're obviously going to see a wider move towards PCIe 4.0 for many devices, of which one of the first will be USB4 host controllers, as you can see above. I don't understand why you think that only Intel can push the ecosystem forward, as they're far from the single driving force in the computer industry, as not all devices are meant for PC use only. There are plenty of ARM based server processors with PCIe 4.0 and Intel isn't even the first company with PCIe 5.0 in their processors.

I think you need to broaden your horizons a bit before making a bunch of claims about things you have limited knowledge about.For several reasons, not just because of PCIe 4.0. As for Z690, the singular PCIe 5.0 slot isn't likely to increase cost in and of itself, as it shouldn't be far enough away from the CPU to require redrivers or any other kind of signal conditioners. The only potential thing that might increase costs marginally would be in case there needs to be a change to even higher quality PCB materials to reduce noise, but I don't think that would be the case compared to a PCIe 4.0 board, as this was one of the other changes compared to PCIe 3.0 boards that increased costs.I guess the problem with SSDs is that PCIe 4.0 x2 gives you about the same performance as PCIe 3.0 x4 and the cost of developing a new controller is higher than continuing to use the already developed products that deliver similar performance. There ought to be benefits in things like notebooks though, as they have limited PCIe lanes. As PCIe 4.0 x2 would be considered a "budget" drive, it seems like the few controllers that are available, are DRAM-less, which isn't all that interesting to me at least.

As you point out, it's kind of frustrating that the PCIe interface couldn't have been designed in a way that it hard "forward" compatibility too, in the sense that a PCIe 4.0 x2 device plugged into a PCIe 3.0 x4 interface could utilise the full bandwidth available, instead of only PCIe 3.0 x2.

That's also why we're stuck with the ATX motherboard standard, even though it's not really fit for purpose any more and barely resembles what it did when it launched. That said, I do not miss AT motherboards...

It's always nice with new, faster interfaces, but in terms of PC technology, we've only just gotten a new standard and outside of NVMe storage, we're just scratching the surface of what PCIe 4.0 can offer. Maybe AMD did a "bad choice" by going with PCIe 4.0 if it's really set to be replaced by PCIe 5.0 so soon, but I highly doubt it, mainly due to the limitations of the trace lengths. PCIe 3.0 is the only standard that doesn't need additional redrivers to function over any kind of distance, at least until someone works out a better way of making motherboards. PCIe 4.0 is just about manageable, but 5.0 is going to have much bigger limitations and 6.0 might be even worse.Actually, you can get a simple adapter from a current PSU to the ATX12VO connector, you just need to discount the 5V and 3.3V when you look at the total Wattage of your PSU.

As such, you might have to discount for 100W or so from the total output of the PSU.