Researchers Build a CPU Without Silicon Using Carbon Nanotubes

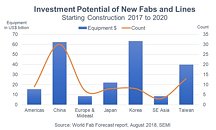

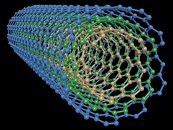

It is no secret that silicon manufacturing is an expensive and difficult process which requires big investment and a lot of effort to get right. Take Intel's 10 nm for example. It was originally planned to launch in 2015, but because of technical difficulties, it got delayed for 2019. That shows how silicon scaling is getting more difficult than ever, while costs are rising exponentially. Development of newer nodes is expected to cost billions of Dollars more, just for the research alone and that is not even including the costs for the setting up a manufacturing facility. In order to prepare for the moment when the development of ever-decreasing size nodes becomes financially and physically unfeasible, researchers are exploring new technologies that could replace and possibly possess even better electrical properties than silicon. One such material (actually a structure made from it) is Carbon Nanotube or CNT in short.

Researchers from MIT, in collaboration with scientists from Analog Devices, have successfully built a CPU based on RISC-V architecture entirely using CNTs. Called RV16X Nano, this CPU is currently only capable of executing a classic "Hello World" program. CNT is a natural semiconductor, however, when manufactured, it is being made as a metallic nanotube. That is due to the fact that metallic nanotubes are easier to integrate into the manufacturing ecosystem. Its has numerous challenges in production because CNTs tend to position themselves randomly in XYZ axes. Researchers from MIT and Analog Devices solved this problem by making large enough surfaces so that enough random tubes are positioned well.

Researchers from MIT, in collaboration with scientists from Analog Devices, have successfully built a CPU based on RISC-V architecture entirely using CNTs. Called RV16X Nano, this CPU is currently only capable of executing a classic "Hello World" program. CNT is a natural semiconductor, however, when manufactured, it is being made as a metallic nanotube. That is due to the fact that metallic nanotubes are easier to integrate into the manufacturing ecosystem. Its has numerous challenges in production because CNTs tend to position themselves randomly in XYZ axes. Researchers from MIT and Analog Devices solved this problem by making large enough surfaces so that enough random tubes are positioned well.