NVIDIA to Introduce an Architecture Named After Ada Lovelace, Hopper Delayed?

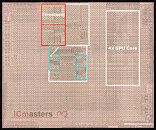

NVIDIA has launched its GeForce RTX 3000 series of graphics cards based on the Ampere architecture three months ago. However, we are already getting information about the next-generation that the company plans to introduce. In the past, the rumors made us believe that the architecture coming after Ampere is allegedly being called Hopper. Hopper architecture is supposed to bring multi-chip packaging technology and be introduced after Ampere. However, thanks to @kopite7kimi on Twitter, a reliable source of information, we have data that NVIDIA is reportedly working on a monolithic GPU architecture that the company internally refers to as "ADxxx" for its codenames.

The new monolithically-designed Lovelace architecture is going make a debut on the 5 nm semiconductor manufacturing process, a whole year earlier than Hopper. It is unknown which foundry will manufacture the GPUs, however, both of NVIDIA's partners, TSMC and Samsung, are capable of manufacturing it. The Hopper is expected to arrive sometime in 2023-2024 and utilize the MCM technology, while the Lovelace architecture will appear in 2021-2022. We are not sure if the Hopper architecture will be exclusive to data centers or extend to the gaming segment as well. The Ada Lovelace architecture is supposedly going to be a gaming GPU family. Ada Lovelace, a British mathematician, has appeared on NVIDIA's 2018 GTC t-shirt known as "Company of Heroes", so NVIDIA may have already been using the ADxxx codenames internally for a long time now.

The new monolithically-designed Lovelace architecture is going make a debut on the 5 nm semiconductor manufacturing process, a whole year earlier than Hopper. It is unknown which foundry will manufacture the GPUs, however, both of NVIDIA's partners, TSMC and Samsung, are capable of manufacturing it. The Hopper is expected to arrive sometime in 2023-2024 and utilize the MCM technology, while the Lovelace architecture will appear in 2021-2022. We are not sure if the Hopper architecture will be exclusive to data centers or extend to the gaming segment as well. The Ada Lovelace architecture is supposedly going to be a gaming GPU family. Ada Lovelace, a British mathematician, has appeared on NVIDIA's 2018 GTC t-shirt known as "Company of Heroes", so NVIDIA may have already been using the ADxxx codenames internally for a long time now.