Yields of Intel Sapphire Rapids Processors Are Low, Mass Production to Start in 1H2023

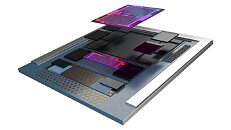

Intel's upcoming Sapphire Rapids processors have faced multiple delays over the past few years. Built on Intel 7 manufacturing process, the CPU is supposed to bring new advances for Intel's clients and significant performance uplifts. However, TrendForce reports that the mass production of Sapphire Rapids processors will be delayed from Q4 of 2022 to the first half of 2023. The reason for this (yet another) delay is that the Sapphire Rapids MCC die is facing a meager yield on Intel 7 manufacturing technology, estimated to be at only 50-60% at the time of writing. Economically, this die-yielding percentage is not profitable for Intel since many dies are turning out to be defective.

This move will stop many OEMs and cloud service providers (CSPs) from rolling out products based on the Sapphire Rapids design and will have to delay it until next year's mass production. On the contrary, AMD is likely to reap the benefits of Intel's delay, and AMD's x86 server market share will jump from 15% in 2022 to 23% in 2023. Given that AMD ships processors with the highest core counts, many companies will opt for AMD's solutions in their data centers. With more companies being concerned by their TCO measures with rising energy costs, favors fall in the hand of single-socket servers.

This move will stop many OEMs and cloud service providers (CSPs) from rolling out products based on the Sapphire Rapids design and will have to delay it until next year's mass production. On the contrary, AMD is likely to reap the benefits of Intel's delay, and AMD's x86 server market share will jump from 15% in 2022 to 23% in 2023. Given that AMD ships processors with the highest core counts, many companies will opt for AMD's solutions in their data centers. With more companies being concerned by their TCO measures with rising energy costs, favors fall in the hand of single-socket servers.