AMD Ryzen 9 5950X 16-core "Zen 3" Processor Overclocked to 6 GHz and Geekbenched

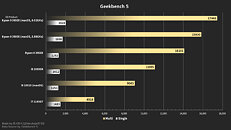

Thai PC enthusiast TUM_APISAK discovered a Geekbench 5 database listing for an upcoming AMD Ryzen 9 5950X "Zen 3" processor, obtained on MacOS. Don't worry, Apple isn't making an AMD-powered iMac Pro as its x86 swansong, because the listing points to a Hackintosh setup using Acidanthera boot-loader. The 5950X engineering sample scores 17448 points multi-threaded, and 2024 points single-core. Here's the best part—the processor appears to be overclocked to 6 GHz, as pointed out in the gb5 files of the benchmark listings, which show the processor's frequency swing between 5931 MHz and 6023 MHz during the test. harukaze5719 compiled a nice bar-graph that compares the 6 GHz overclocked 5950X "Zen 3" to 5.88 GHz overclocked 3950X "Zen 2," and other processors in its class, such as the Core i9-10900K. Find the Geebench listing here.