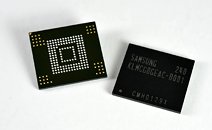

Intel "Ice Lake-U" Gen 11 iGPU Features 48 Execution Units

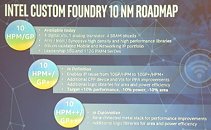

Intel's next generation "Ice Lake" processor could integrate a significantly faster integrated graphics solution (iGPU), if a SiSoft SANDRA online database entry is to be believed. A prototype "Ice Lake" chip was benchmarked, with its iGPU being described by the database as "Intel UHD Graphics" based on the company's Gen 11 graphics architecture, which succeeds the current Gen 9.5 architecture implemented on "Coffee Lake" and "Kaby Lake." This iGPU is endowed with 48 execution units (EUs), which work out to 384 unified shaders; against 24 EUs and 192 shaders on Intel UHD 620. SANDRA also describes the iGPU as being able to share up to 6 GB of memory from the system memory; and featuring 768 KB of dedicated cache. Its reference clock is 600 MHz, double that of the UHD 620, although its boost clock remains a mystery. "Ice Lake" is being built on Intel's new 10 nm+ silicon fabrication process, so it's understandable for the company to significantly enlarge its iGPU.