Intel Says Its Upcoming Gen12 GPUs Will Feature Biggest Architecture Change In A Decade

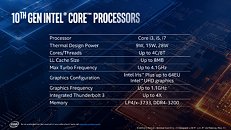

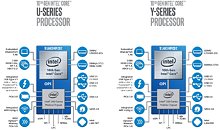

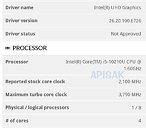

Intel is slowly realizing plans to "one up" its GPU game starting from first 10 nm Ice Lake CPUs that feature Gen11 graphics, equipping users of integrated GPUs with much more performance than they previously got. Fortunately, Intel doesn't plan to stop there. Thanks to the recent pull request found on GitLab Mesa repository, we can now expect to receive biggest GPU performance bump in over a decade with the arrival of Gen12 based GPUs, found on next generation Tiger Lake processors.

In this merge request, Francisco Jerez, member of Intel's open source Linux graphics team, stated the following: "Gen12 is planned to include one of the most in-depth reworks of the Intel EU ISA since the original i965. The encoding of almost every instruction field, hardware opcode and register type needs to be updated in this merge request. But probably the most invasive change is the removal of the register scoreboard logic from the hardware, which means that the EU will no longer guarantee data coherency between register reads and writes, and will require the compiler to synchronize dependent instructions anytime there is a potential data hazard..."

In this merge request, Francisco Jerez, member of Intel's open source Linux graphics team, stated the following: "Gen12 is planned to include one of the most in-depth reworks of the Intel EU ISA since the original i965. The encoding of almost every instruction field, hardware opcode and register type needs to be updated in this merge request. But probably the most invasive change is the removal of the register scoreboard logic from the hardware, which means that the EU will no longer guarantee data coherency between register reads and writes, and will require the compiler to synchronize dependent instructions anytime there is a potential data hazard..."