TSMC is Ramping Up 7nm Production, 5nm Next Year

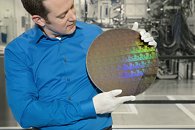

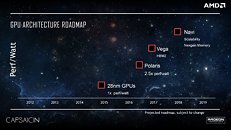

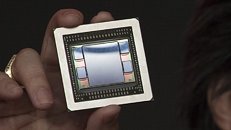

At their technology symposium in Taipei, TSMC CEO CC Wei has made remarks, dismissing speculation that their 7 nanometer yield rate was not as good as expected. Rather the company is ramping up production capacity for 7 nm quickly, up 9% from 10.5 million wafers in 2017, to 12 million wafers in 2018. They plan to tape out more than 50 chip designs in 2018, with the majority of the tape outs for AI, GPU and crypto applications, followed by 5G and application processors.

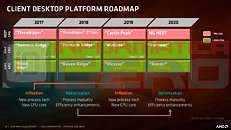

Most of their orders for the 7 nanometer node come from big players like AMD, Bitmain, NVIDIA and Qualcomm. Apple's A12 processor for upcoming iPhones is also a major driver for TSMC's 7 nanometer growth. These orders will be fulfilled in early 2019, so it'll be a bit longer before we have 7 nm processors for the masses.

Next-gen 5 nanometer production will kick off next year, followed by mass production in late 2019 or early 2020. The company will invest as much as USD 25 billion in their new production facilities for this process node.

Most of their orders for the 7 nanometer node come from big players like AMD, Bitmain, NVIDIA and Qualcomm. Apple's A12 processor for upcoming iPhones is also a major driver for TSMC's 7 nanometer growth. These orders will be fulfilled in early 2019, so it'll be a bit longer before we have 7 nm processors for the masses.

Next-gen 5 nanometer production will kick off next year, followed by mass production in late 2019 or early 2020. The company will invest as much as USD 25 billion in their new production facilities for this process node.