AMD to Detail Zen 2, Navi Architectures Come Hot Chips in August

The Hot Chips conference is one of the leading-edge grounds for discussion of new silicon-bound technologies, and AMD will, as usual, take to its grounds in an effort to detail their efforts in their technology fields. The conference's organization has already confirmed a number of participants in its conference schedule, which includes the likes of Intel, Microsoft, Alibaba, NVIDIA, Tesla and of course, AMD.

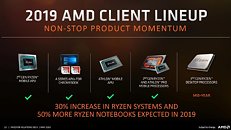

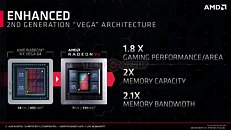

AMD will be delivering two keynotes: the first, on August 19th, is simply titled "Zen 2", and will therefore deal with the underpinnings of the Zen 2 microarchitecture, which will be pervasive to all of AMD's CPU product lines. A second conference will be held on the same day by AMD's CEO Lisa Su herself, and is titled "Delivering the Future of High-Performance Computing with System, Software and Silicon Co-Optimization". On the next day, August 20th, another AMD keynote is simply titled "7 nm Navi GPU", and we expect it to follow in the footsteps of the Zen 2 conference. So, with AMD diving deep into both architectures come August... it's extremely likely the company will have launched both product lines by then. Fingers crossed. You can find the abstract on AMD's CEO Lisa Su's conference after the break.

AMD will be delivering two keynotes: the first, on August 19th, is simply titled "Zen 2", and will therefore deal with the underpinnings of the Zen 2 microarchitecture, which will be pervasive to all of AMD's CPU product lines. A second conference will be held on the same day by AMD's CEO Lisa Su herself, and is titled "Delivering the Future of High-Performance Computing with System, Software and Silicon Co-Optimization". On the next day, August 20th, another AMD keynote is simply titled "7 nm Navi GPU", and we expect it to follow in the footsteps of the Zen 2 conference. So, with AMD diving deep into both architectures come August... it's extremely likely the company will have launched both product lines by then. Fingers crossed. You can find the abstract on AMD's CEO Lisa Su's conference after the break.